随着集成电路的发展和数字信号处理技术的采用,数字示波器已成为集显示、测量、运算、分析、记录等各种功能于一体的智能化测量仪器。数字示波器在性能上也逐渐超越模拟示波器,并有取而代之的趋势。与模拟示波器相比,数字示波器不仅具有可存储波形、体积小、功耗低,使用方便等优点,而且还具有强大的信号实时处理分析功能。因此,数字示波器的使用越来越广泛。目前我国国内自主研发的高性能数字示波器还是比较少,广泛使用的仍是国外产品。因此,有必要对高性能数字示波器进行广泛和深入研究。

本文通过采用高速高性能器件,设计了一实时采样率为60 msa/s的宽带数字示波器。

1 数字示波器的性能参数设计数字存储示波器的指标很多,包括采样率、带宽、灵敏度、通道数、存储容量、扫描时间和最大输入电压等。其中关键的技术指标主要有采样率、垂直灵敏度(分辨率)、水平扫描速度(分辨率)。这几项指标直接与所选a/d、fifo和高速运放器件的性能,以及电路设计有关。下面根据所选器件的性能参数,合理地分析和确定示波器的采样率和分辨率。

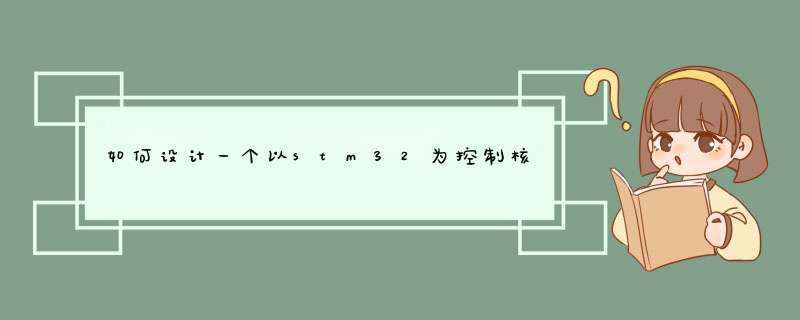

1.1 采样率与水平扫描分辨率采样率主要取决于a/d转换器的转换速率,常用每秒取样点数sa/s(sample/second)来表示。本系统设计最高实时采样率为60msa/ s,若进一步提高采样率可采用文献提出的等效采样技术,不过等效采样技术的软硬件和价格成本很高。为了使示波器具有较高的信号波形分析细节,采用数字内插技术来恢复和重建信号波形。文献中详细论述了线性内插和正弦内插算法在示波器设计中的应用问题。因此,对这两种内插算法不再详细论述,在本文设计中直接引用文献中的研究成果。根据文献研究结果,取信号每周期采样点数为20,插值倍数为4。水平显示像素点数为400个,共10格。水平扫速与采样时钟频率的关系表如下。

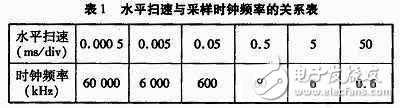

垂直分辨率的高低直接影响数字示波器对波形细节的显示,垂直分辨率越高,则示波器上的信号波形细节越小,它取决于a/d转换精度和tft的显示分辨率。本文设计中取最大采样输入电压为2 vpp,垂直刻度为8格,共256个像素点,因此垂直精度为0.25 v/格。共设计9个灵敏度档位,每档灵敏度与程控放大倍数的关系如表2所示。

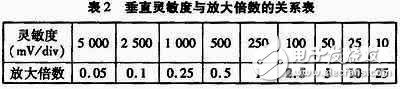

系统硬件总体框图如图1所示,主要由stm32控制单元,信号输入阻抗匹配单元,信号调理单元,a/d采样与fifo存储单元,时钟单元,tft显示单元等组成。输入信号经阻抗匹配后,送入信号调理单元,将信号的幅度放大或衰减到适合a/d采样的范围内,a/d采样单元对幅度为2vpp的信号进行a/d采样,并将采样结果存入fifo单元中。cpu从fifo中读存数据并进行内插运算,然后根据用户通过键盘输入的指令将信号波形显示在tft液晶屏上。另外,cpu还可以将数据通过rs232接口上传给上位机,或进行打印等处理。

对于低速数据采集,由于信号反射对信号的传输过程影响微乎其微,所以低速数据采集系统良好的高阻抗性能,对提高系统的测量精确度有很大的意义。本设计中采用电压跟随器实现阻抗变换,数据采集阻抗变换电路的设计方案如图2所示,其输入阻抗为10mω。

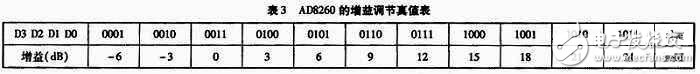

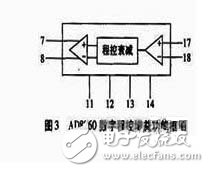

信号调理电路主要采用具有可变增益的数字程控放大器ad8260。ad8260是ad公司生产的一款大电流驱动器及低噪声数字可编程可变增益放大器。该器件增益调节范围为-6 db~+24 db,可调增益的-3 db带宽为230mhz,可采取单电源或双电源供电。主要用于数字控制自动增益系统、收发信号处理等领域。本设计主要使用其数字控制自动增益功能。ad8260内部的数字程控增益功能框图如图3所示。经阻抗匹配后的信号可直接输入ad8260的17、18脚,经ad8260内部前端放大器6 db的固定增益放大,-30 db程控衰减以及末级放大器18 db固定增益放大后,由7和8脚输出。第11、12、13、14脚为四位数字控制信号(d0、d1、d2、d3),与stm32的i/o口直接连接,实现增益控制。表3给出了ad8260增益调节真值表。

在数据采集电路设计中,选用bb公司的8位高速ad转换器ads830e,最高采样频率为60 msa/s,最低采样频率为10 ksa/s。8位转换精度的显示分辨率为256格,能够满足所选用分辨率为640*480的tft显示模块。fifo存储器采用idt7204高速缓存,其缓存深度达1 024 k。fifo存储器是一种双口的sram,没有地址线,随着写入或读取信号对数据地址指针进行递加或递减,来实现寻址。

2.5 时钟电路时钟产生电路为ad转换器提供一系列的采样时钟信号,共有8种频率,分别对应着不同的水平扫速。时钟产生电路主要由高稳定度的温补晶振,分频器74ls390,多路选择器74f151以及分频器74f74触发器构成。基准时钟信号由一块60 mhz的温度补偿型有源晶体模块提供,输出的60 mhz信号经过分频器的多次分频得到8种不同的频率,然后送入多路选择器74f151。stm32通过对74f151的三根选通信号线进行控制来选择所需的采样频率。另外,中央控制器采用stm32处理器,主频设为80 mhz。显示器采用分辨率为640*480的tft显示模块,与stm32之间采用spi接口。与其它上位机通信采用rs232口。

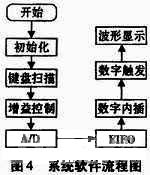

3 系统软件设计系统软件设计采用模块化设计方法,整个程序主要由初始化程序、人机交互菜单程序、键盘扫描程序、触发程序、显示程序和数据采集及频率控制程序组成。系统软件的流程图如图4所示。

在实验室对研制的样品机进行了测试实验,图5和图6分别显示了频率为16.2 khz和1 khz的方波信号。由测试数据分析可得:垂直灵敏度满足要求,电压测量误差≤5%,输入端输入阻抗大于2 mω,实验结果达到了设计要求。

为实现一个高采样率,宽频带的便携式数字存储示波器,设计了以stm32为控制核心的数字示波器。硬件平台主要采用了ad8260数字程控增益放大器作为前端信号调理电路,ads830高速宽带模数转换器和idt7204高速缓存作为数字采集电路,以及信号波形采用了tft彩屏显示。另外,通过采用数字内插的数字信号处理算法来重建和还原信号波形,进而改善了信号波形显示细节。最后对研制样品进行了实验室测试,实验结果表明硬件设计思路与软件及算法的处理是正确的,性能参数达到设计要求,可以应用在工程实践中。

数字示波器在信号显示,处理以及带宽等方面比传统模拟示波器更有优势,因此数字示波器是今后示波器发展的重要方向。本文采用stm32高性能arm处理器作为核心控制芯片,能够满足tft彩色波形显示,数字插值算法处理等。通过采用高速ad和fifo器件,实现了高采样率,宽频带的技术要求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)