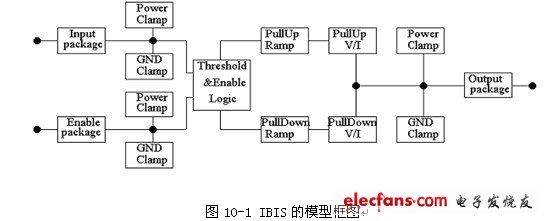

仿真设计可行性和有效性取决于模型的建立,本章在介绍SPICE仿真模型基本原理及其存在的主要问题的基础上,重点介绍IBIS模型原理和应用。

10.1 SPICE仿真模型原理与使用

10.1.1 SPICE模型概述

Spice(SimulaTIon Program with integrated CircuTI Emphasis)是一种通用电路分析程序,能够分析和模拟一般条件下的各种电路特性。

Spice的发展已有30多年的历史。20世纪60年代中期,IBM公司开发了ECAP程序。以此为起点,美国加州伯克利大学分校于60年代末开发了CANCER电路分析程序,并在此基础上,于1972年推出了Spice程序。1975年后,伯克利大学又相继推出了升级版。Spice源程序是开放的,能够迅速的进行扩展和改进,使得它的电路分析功能不断扩充,算法不断完善,元器件和模型不断增加和更新,分析精度和运行时间也得到有效的改善,因而成为工业和科研上电路模拟的标准工具。

Pspice是Spice家族的一员,其主要算法与Spice相同。它是美国Microsim公司于1984年推出的。随着版本的升级,Pspice的功能不断完善,具有高超的电路仿真能力。

本文全部内容详见:https://www.elecfans.com/soft/35/2012/20120529274141.html

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)