本文主要解读STM32低功耗模式的机制,并不侧重STM32低功耗的程序实现,而且借助STM32固件库实现STM32低功耗会变的非常简单。

一、STM32芯片性能

使用芯片型号:stm32f030f4,CORTEX-M0.封装TSSOP20.

运行模式:内部时钟(HSI),系统时钟频率采用48MHZ。

工作电压:3.3V

芯片具体参数如下:

二、芯片功耗

功耗:

芯片工作模式:

工作模式:外设正常运行,内核CPU及SRAM供电,未使用外设的时钟默认关闭。

睡眠模式:只有CPU停止工作,各个外设正常工作,依靠任何中断/事件唤醒。

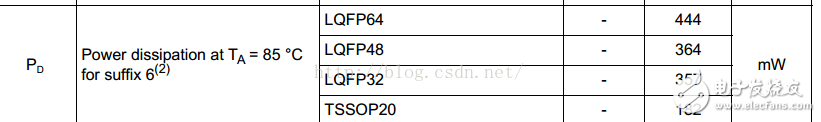

停机模式:1.8V供电区域时钟被停止,内部HSI,PLL,外部时钟HSE均关闭,同时电压检测器也可进入低功耗模式,但SRAM和寄存器不断电,此时只能依靠外部中断(EXTI)和RTC时钟才能唤醒。

待机模式:1.8V供电区域被时钟停止,内部HSI,PLL,外部时钟HSE均关闭,同时电压检测器也可进入低功耗模式,SRAM和不属于待机电路的寄存器也被断电关闭,此时即使是外部中断(EXTI)也不能将其唤醒,只能通过复位(外部复位,看门狗复位)、唤醒引脚、RTC时钟来唤醒。

注意:无论是在停止模式还是待机模式下,RTC和IWDG及其时钟源不会被关闭。

各个模式功耗:

功耗计算方式:功耗=工作电压*工作电流。

静态损耗:

内部上下拉电阻损耗:这部分损耗主要取决于内部电阻的大小,一般为了降低内部电阻损耗常常需要降低电阻两端电压,若引脚为低电压则采用下拉电阻,若引脚为高电压则采用上拉电阻。

I/O额外损耗:当引脚设为输入I/O时,用来区分电压高低的斯密特触发器电路会产生一部分消耗,为此可将引脚设为模拟输入模式。

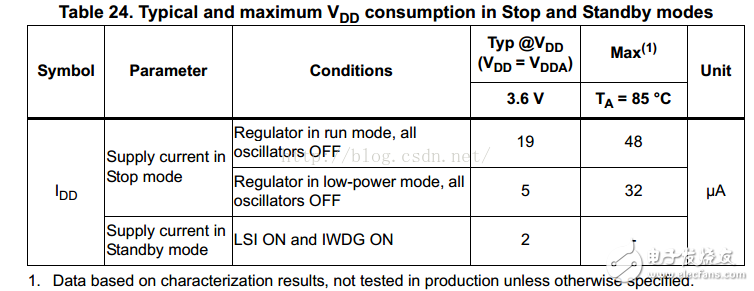

动态损耗:对于悬浮的引脚,由于其电压不稳定会产生外部电磁干扰和损耗,因此必须把悬浮引脚设为模拟模式或输出模式,引脚电压的切换会对外部和内部电容负载产生动态损耗,其损耗与电压切换频率和负载电容有关。具体损耗值如下:

三、CORTEX-M0低功耗功能、指令、相关寄存器

CORREX内核支持低功耗模式有2种:

睡眠模式:CPU时钟停止,对应STM32睡眠模式

深度睡眠模式:系统时钟停止,PLL,FLASH关闭,对应STM32停机模式。

进入睡眠模式:

当CPU处理完中断后软件必须能使其进入睡眠模式,当CPU执行WFI指令,其将会立即进入睡眠模式,当异常产生或中断被挂起时,其立即被唤醒。

当CPU执行WFE指令时,它首先会检查对应的事件标志位,当事件标志寄存器为0时进入睡眠模式,否则将寄存器事件标志清0并继续执行程序。事件标志可由外部事件标志或SEV指令产生。

返回方式:通过设置内核SCB寄存器的Sleep-on-exit位,可以选择系统被唤醒执行完中断服务程序后进入主线程模式后是否立即进入睡眠模式。

从睡眠中唤醒:

WFI唤醒或sleep-on-exit:

一般来说,使能的异常可以唤醒内核。对于一些系统,在唤醒后执行中断处理程序前需要先执行重新恢复的任务,则首先需要屏蔽所有中断(PRIMASK=1),中断发生后内核被唤醒但不执行中断处理,待执行完恢复任务后再将PRIMASK设为0,此后执行中断处理任务。

WFE唤醒:

使能异常可以唤醒内核。外部事件或SEV指令发送的事件也可唤醒内核。

注意:当SCR的SEVONPEND设置为1时,任何使能/非使能中断或事件都可唤醒内核。

中断唤醒控制器(WIC):

WIC只有在SCR寄存器DEEPSLEEP位设为1时才能使能,WIC不可编程也没有相关的控制寄存器,它仅与硬件信号有关,当进入深睡眠时内核大部分模块被关闭,系统计数器也被关闭,因此当内核被唤醒时需要较多的时间恢复到睡眠前的状态并处理中断。

外部事件输入:可在WFE模式下唤醒内核。

相关指令:

WFE等待事件,若无事件则睡眠,中断、事件唤醒

WFI等待中断,立即进入睡眠,中断唤醒

SEV软件发送一个事件,在核系统中可唤醒另一个内核。

微控制器软件接口标准:

由指令对应的C语言接口:

//core_cmInstr.h

void__WFE(void)//WaitforEvent

void__WFI(void)//WaitforInterrupt

void__SEV(void)//SendEvent

相关寄存器:

SCR寄存器:

SEVONPEND:

0:只有使能的中断或事件才能唤醒内核。

1:任何中断和事件都可以唤醒内核。

SLEEPDEEP:

0:低功耗模式为睡眠模式。

1:进入低功耗时为深度睡眠模式。

SLEEPONEXIT:

0:被唤醒进入线程模式后不再进入睡眠模式。

1:被唤醒后执行完相应的中断处理函数后进入睡眠模式。

四、STM32时钟管理

运行模式下可通过关闭和降低相关外设的时钟频率来减少功耗。

APB外设时钟和DMA时钟可用软件禁止。

睡眠模式停止CPU时钟。在CPU睡眠中存储器接口时钟(Flash和RAM接口)可被停止。当连接到APB所有外设的时钟禁止后,当进入睡眠期间AHB到APB桥时钟由CPU的硬件关闭。

CPU进入停止模式时停止V18域、PLL、HSI、HSI14和HSE振荡器的时钟。

HDMICEC,USART1和I2C1即使在MCU进入停止模式下仍有能力打开HIS振荡器(假如HIS被选为这些外设的时钟)。

在LSE振荡器已使能的情况下,HDMICEC和USART1当在系统进入停止模式下也可由LSE振荡器驱动(假如LSE被选为这些外设时钟)。但是这些外设没有打开LSE振荡器的能力。

CPU进入待机模式时停止V18域、PLL、HSI、HSI14和HSE振荡器的时钟。

当设置DBGMCU_CR寄存器中的DBG_STOP或DBG_STANDBY位,那么CPU在相应的深度睡眠模式下也可以具有调试功能。

当系统由中断(停止模式)或复位(待机模式)唤醒后,HSI振荡器被选为系统时钟(不管进入停止模式或待机模式前选用的是何种时钟)。

假如当前正在进行闪存编程,只有在闪存编程全部完成之后才会进入深度睡眠模式(深度睡眠延后)。若当前正在使用APB域,那么只有全部完成APB域的 *** 作后才进入深度睡眠模式。

五、STM32低功耗设置

STM32工作模式主要有运行、睡眠、停止、待机4种模式。

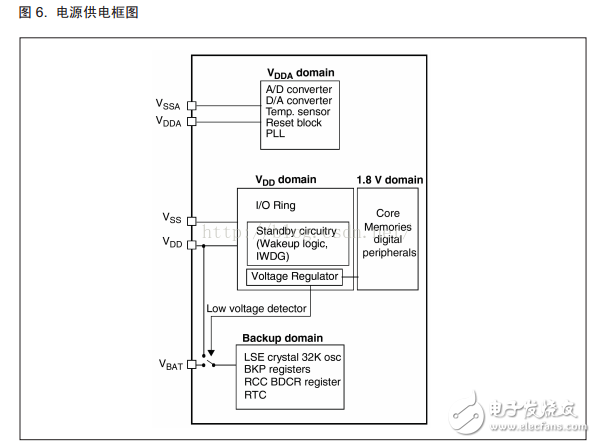

供电框图

由上图可以看到整个STM32芯片的供电图,模拟电路部分采用VDDA独立供电,各个部分可以独立被关断或开启。备份电路部分由电池供电,主要有RTC时钟及相关的备份寄存器,VDD掉电后可由电池供电,对于没有VBAT引脚的芯片,其电源直接与VDD相连。核心部分分为1.8V工作域和VDD工作域,1.8V工作域主要有内核、存储、外设部分,VDD供电域主要有I/O、待机电路(唤醒电路,独立看门狗)、电压调节器(VoltageRegulator)。

电压调节器

器件复位后电压调节器总是打开着的,其根据应用模式有三种不同的工作模式。

运行模式:调节器以全功耗模式为域(内核,内存和数字外设)提供1.8V电源。

停止模式:调节器以低功耗模式为保持寄存器及SRAM数据部分域提供1.8V的电源。

待机模式:调节器断电,除了待机电路及备份域电路外,寄存器和SRAM的内容全部丢失。

相关寄存器介绍:

1,cortex-mo中的SCR寄存器

SEVONPEND:

0:只有使能的中断或事件才能唤醒内核。

1:任何中断和事件都可以唤醒内核。

SLEEPDEEP:

0:低功耗模式为睡眠模式。

1:进入低功耗时为深度睡眠模式。

SLEEPONEXIT:

0:被唤醒进入线程模式后不再进入睡眠模式。

1:被唤醒后执行完相应的中断处理函数后进入睡眠模式。

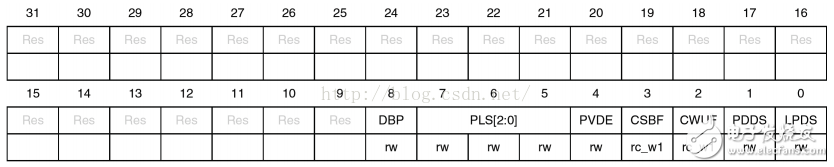

2,电源控制寄存器PWR_CR

其中与低功耗有关的控制位:

CSBF:清除待机标志,该位始终读出为0,写1清除待机标志。

CWUF:清除唤醒标志,该位始终读出为0。写1清除唤醒标志。

PDDS:掉电深睡眠

0:当CPU进入深睡眠时进入停机模式,调压器的状态由LPDS位控制。

1:当CPU进入深睡眠时进入待机模式。

LPDS:深睡眠下的低功耗

0:在停机模式下电压调节器开启

1:在停机模式下电压调节器处于低功耗模式

3,电源控制/状态寄存器(PWR_CSR)

EWUP2/EWUP1:使能WKUP2或EWUP1引脚。

0:WKUP1/2引脚作为通用IO口。WKUP1引脚上的事件不能将CPU从待机模式唤醒。

1:WKUP1/2引脚用于将CPU从待机模式唤醒,WKUP1引脚被强置为输入下拉的配置(WKUP1引脚上的上升沿将系统从待机模式唤醒)。

SBF:待机标志

该位由硬件设置,只能设置电源控制寄存器PWR_CR的CSBF位清除。

0:系统不在待机模式

1:系统进入待机模式

WUF:唤醒标志

由硬件设置,只能设置电源控制寄存器PWR_CR的CWUF位清除。

0:没有唤醒事件发生

1:从WKUP或RTC闹钟产生一个唤醒事件

注意:当WKUP引脚已经是高电平时,在(通过设置EWUP位)使能WKUP引脚时,会检测到一个额外唤醒的事件。

低功耗模式的进入与退出问题

1、睡眠模式

进入睡眠模式:

当STM32在运行状态时,执行WFI或WFE指令可进入睡眠模式。

条件:SLEEPDEEP=0,设为睡眠模式。此时CPU时钟被停止。

若令被唤醒的STM32执行完中断处理任务后进入睡眠模式,则可将SLEEPONEXIT设为1.

退出睡眠模式:

执行WFI指令进入睡眠,可通过使能中断唤醒。执行WFE指令进入睡眠可由事件唤醒,CPU时钟打开。产生事件的两种方式:

配置一个外部或内部EXTI线做为事件模式。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)