JESD204B 协议中的三个状态对于在链路的 TX 和 RX 之间构建有效数据链路非常重要,它们是:代码组同步 (CGS)、初始信道对齐序列 (ILAS) 和用户数据。今天我将探讨在 TX 与 RX 之间必然会出现的信号发送技术,完成构建有效链路所需的必要步骤。

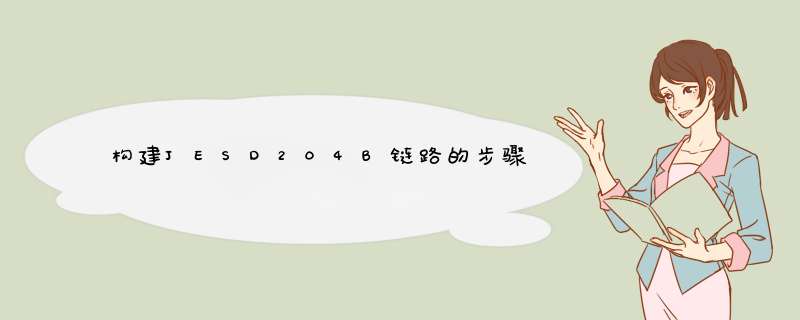

图 1 — JESD204B TX 至 RX 链路的信号连接

从 TX (tx_dataout) 到 RX 的信号是包含数据链路的串行解串器信道信号。这些信号不需要偏移对齐。从 RX 回到 TX 的信号是 SYNCn 请求信号。

时钟芯片通常是 LMK04828 超低抖动合成器与抖动清除器,可为 txlink_clk 和 rxlink_clk 提供一个器件时钟。此外,它还可提供用来同步 TX 和 RX 时间域的 SYSREF。

发送器和互补的接收器包含 8b/10b 编码、数据链路层、扰频器和传输层。我们假设发送器和接收器都采用相同的 LMFS 配置和 PLL 设置。

要在经过 JESD204B 协议的各个状态时检验信号,可使用 FPGA 厂商提供的信号分析工具。

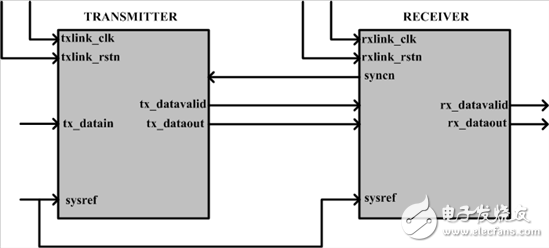

构建 JESD204B 链路的第一步是 RX 发信号通知 TX 开始代码组同步 (CGS):

a.) RX 针对 TX 降低 SYNC 信号,请求执行 CGS。

b.) TX 的回应将是开始发送 K28.5 字符(8b/10b 编码之前的 0xBC 十六进制)。

c.) RX 接收到并最少解码 4 个 K28.5 字符后,它会提高 SYNC 信号,让 TX 开始发送 ILAS 序列。

图 2 — a) 从 RX 到 TX 的 SYNC 低信号请求;b) TX 以 K28.5(0xBC 八位位组)作为回应;c) 在 RX 收到 K28.5 字符后,SYNC 被提高,使 TX 开始发送 ILAS

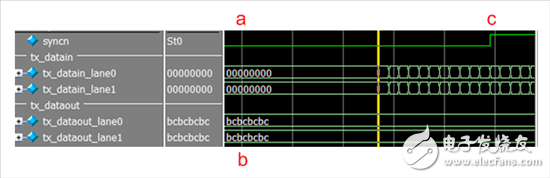

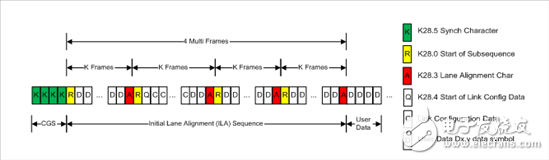

下一步是初始信道对齐序列 (ILAS):

d.) 一旦 SYNC 升高,TX 就会在本地多帧时钟(LMFC,LMFC 在图中未显示)的上升沿位置的每个信道上发送 ILAS 信号。所有信道都将从源头与该 LMFC 边沿对齐。

e.) ILAS 总是包含 4 个多帧数据。每个多帧数据都以一个 K28.0 字符开始,以一个 K28.3 字符结束。链路配置数据在第 3 个八位位组开始的位置通过第二个多帧数据发送。

图 3 — d) SYNC 被 RX 提高,以告知 TX 开始 ILAS;e) 通过所有信道发送 ILAS

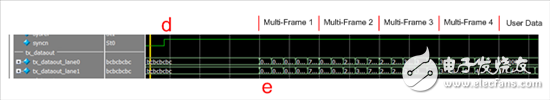

f.) 图 4 概括说明了 ILAS 多帧数据的结构,这可在 TX 发出的 ILAS 八位位组数据流中证实。K28.0=R 和 K28.3=A 字符可用来对齐多点链路中的所有信道。

图 4. ILAS 结构

完成 ILAS 后,TX 将通过串行信道发送有效用户数据。

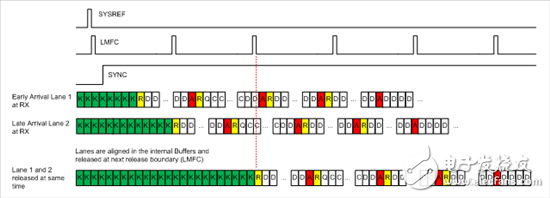

g.) 在 RX 内部,每个信道都会在每个信道的d性缓冲器中存储 ILAS 序列的最后一个 A 字符以及紧跟其后的任何用户数据。d性缓冲器中用户数据的释放点通常是在检测到每个信道d性缓冲器中最后一个 A 字符后的下一个 LMFC 上升沿。接收到的用户数据就像在 TX 侧一样,将需要通过传输层的背面,将串行位重新排列为有意义的并行样片。

h.) 该信道对齐特性可确保来自每个信道的所有数据都可对齐。此外,它还可承受物理布局导致的任何信道偏移。这是在实现确定时延(该主题我将在以后的博客中介绍)过程中所使用的重要特性之一。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)