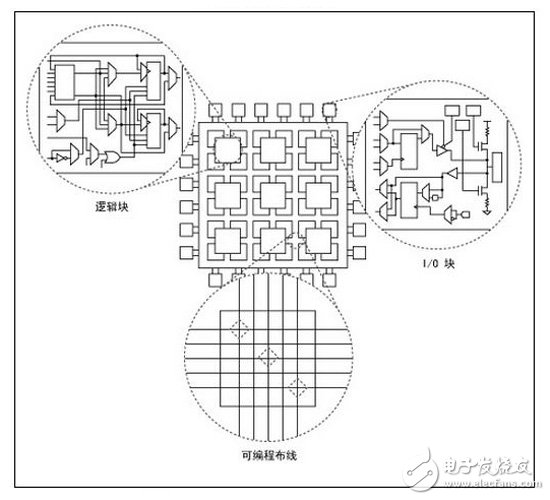

每个FPGA芯片(FPGA)是由有限个带有可编程连接预定义资源组成。这些互连资源通过LabVIEW FPGA模块实现用户设计的数字电路。用户创建FPGA VI时设计一个电路示意图,以说明FPGA逻辑块的连接方式。编译VI时编译工具将FPGA VI转换为FPGA电路。

注: 本主题包含底层FPGA的实现概述。理解上述概念并非为入门LabVIEW FPGA模块的必需要求,但对于用户创建更为有效的FPGA VI可能有所帮助。

设计FPGA应用时,下列FPGA规范为重要的考虑因素。

.可配置的逻辑块数量

.固定函数逻辑块的数量(例如,乘法器)

.存储器资源的大小(例如,嵌入式块RAM)

关于FPGA基础的更多信息,见。

逻辑资源为FPGA上可执行逻辑函数的资源。逻辑资源被组合在片内,以创建可配置逻辑块。每个逻辑片包含一组LUT、触发器和多路复用器。每个LUT是硬接线在FPGA上的逻辑门的集合,UT是存储每个输入组合的预定义输出列表的逻辑块,因此能够快速获取逻辑 *** 作的输出。触发器是由能够实现2个稳态并以单个位表示的电路组成。多路复用器(通常称为MUX)为在两个或更多输入端进行选择并输出选中输入端的电路。

不同的FPGA系列执行逻辑片和LUT的方式不同。例如,Virtex-II FPGA上的逻辑片带有两个LUT和两个触发器。Virtex-5 FPGA上的逻辑片带有四个LUT和四个触发器。此外,LUT的输入端数量通常为2至6个,实际数量取决于FPGA系列。

寄存器

寄存器是存储位模式的一组触发器。FPGA上的寄存器带有时钟、输入数据、输出数据和启用信号端口。在每个时钟周期内,输入数据被触发且存储在内部,然后更新输出数据为与内部存储数据匹配的值。FPGA VI使用寄存器执行下列函数:

.在循环计数间保持状态

.I/O同步

.时钟域间的握手数据

.流水线

.与主控VI通信

寄存器是了解FPGA VI的定时考虑因素的重要概念。

块RAM或块存储器是嵌入在FPGA上用于存储数据的RAM。通常,LabVIEW使用块存储器实现存储器和FIFO函数。 用户可指定LabVIEW分别使用FIFO属性和存储器属性对话框实现FIFO和存储器项。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)