触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种。

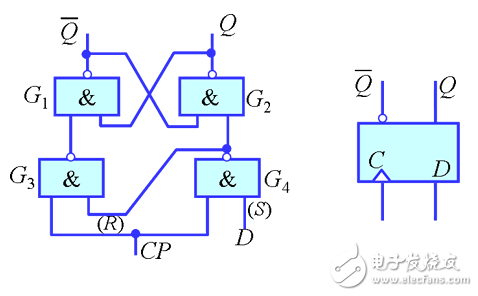

D触发器在时钟脉冲CP的前沿(正跳变0→1)发生翻转,触发器的次态取决于CP的脉冲上升沿到来之前D端的状态,即次态=D。因此,它具有置0、置1两种功能。由于在

CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等。

今日偶然看到一些知名企业的笔试试题,随便扫描了下,看到有几道关于FPGA/CPLD的题目,小小的编程题,用VerilogHDL或VHDL语言编触发器,脑袋转了一下,模糊似乎清晰,清晰又像浸入模糊,呵呵。。。上半年,由于Boss项目,学习了FPGA,学的有点急,也断断续续的,才过几个月,似乎知识已经远去,打开电脑,速览以前的资料,记忆又回来了。。。简单记录下这道题,权当回忆。。。

//基本D触发器

module D_EF(Q,D,CLK)

input D,CLK;

output Q;

reg Q; //在always语句中被赋值的信号要声明为reg类型 寄存器定义

always @ (posedge CLK) //上升沿,下降沿用negedge表示,^_^ 需要记忆

begin Q 《= D; end

endmodule

//带异步清0、异步置1的D触发器

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;//寄存器定义

always @ (posedge clk or negedge set or negedge reset)

begin

if(!reset) begin q《=0;qn《=1;end//异步清0,低有效

else if(!set) begin q《=1;qn《=1;end //异步置1,低有效

else begin q《=~d;qn《=~d;end

end

endmodule

//带同步清0、同步置1的D触发器

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;

always @ (posedge clk)

begin

if(reset) begin q《=0;qn《=1;end//同步清0,高有效

else if(set) begin q《=1;qn《=1;end //同步置1,高有效

else begin q《=~d;qn《=~d;end

end

endmodule

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)