摘要:针对大容量固态存储器中数据错“位”的问题,目前大多采用软件ECC 模型进行检错和纠错,但这势必会极大地影响存储系统的读写性能。基于ECC 校验原理,提出一种并行硬件ECC 模型,并采用FPGA 实现。仿真分析和实验结果表明:该模型不仅具有良好的纠错能力,而且显著地提高了存储系统的读写性能。

由于NAND Flash 生产工艺的局限性,芯片在数据存储或传输过程中偶尔会发生“位”翻转现象,需要进行必要的检错和纠错。常用的数据检验方法有奇偶校验和CRC 校验等[1]。但NAND Flash 出错时一般不会造成整个块( block) 或是页( page) 全部出错,而是其中1 位或几位出错,故在NAND Flash处理中常采用专用的ECC( Error Checking and CorrecTIng)校验。

传统的ECC 校验方法一般采用软件实现,这虽然复杂度低,易于实现工程应用,但由于每次读写NAND Flash 时都需要进行ECC 校验 *** 作,大量的计算校验工作带来庞大的软件开销,直接导致存储系统的读写性能下降。

本文基于高速大容量固态存储器的硬件结构[2],结合NAND Flash 整页读写访问的特点[3],采用FPGA 逻辑进行了硬件方式的设计与实现,提出了一种并行硬件ECC 模型,将ECC 校验和数据读写同时并行实现,既保证了数据的可靠性,又显著地提高了存储系统的读写性能。

1 软件ECC 模型ECC 校验[4,5]是在奇偶校验的基础上发展而来的,它将数据块看作一个矩阵,利用矩阵的行、列奇偶信息生成ECC 校验码。它能够检测并纠正1 位错误和检测2 位错误,克服了传统奇偶校验只能检出奇数位出错、校验码冗长及不能纠错的局限性。

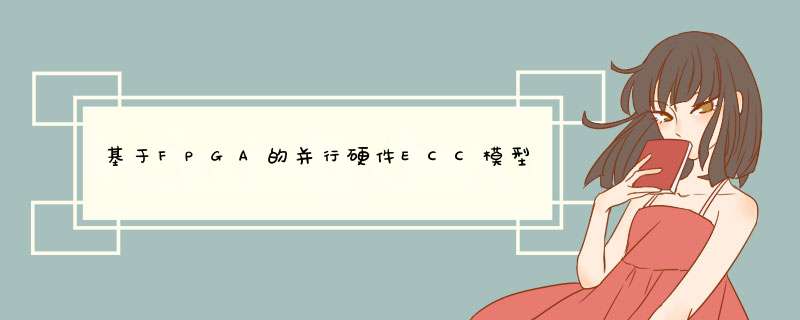

如图1 所示,传统软件ECC 模型的工作机理是:当应用程序需要写数据时,文件系统首先作相应的处理,然后根据待写的数据生成ECC 校验码,接着将数据和ECC 校验码移入数据缓冲区( 硬件Buffer) 中,最后向硬件控制器发起写命令,将数据写入NANDFlash 芯片。读 *** 作的过程刚好逆向执行。

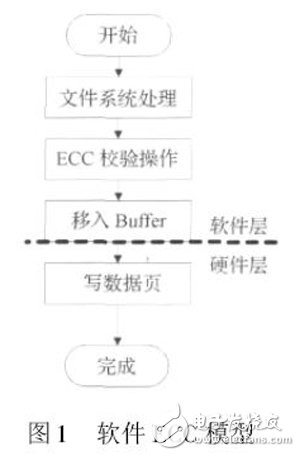

在软件ECC 模型中,首先ECC 校验 *** 作带来庞大的软件开销,直接导致存储系统的读写性能下降。其次向NAND Flash 芯片写入或者读取数据都是以页为单位进行的。本文基于这两点原因,提出了并行硬件ECC 模型( 简称并行ECC 模型) ,如图2 ( b) 所示。一方面,ECC 校验改由硬件实现,减轻了软件开销; 另一方面,读写数据页和ECC 校验并行执行的巧妙设计提高了读写效率。

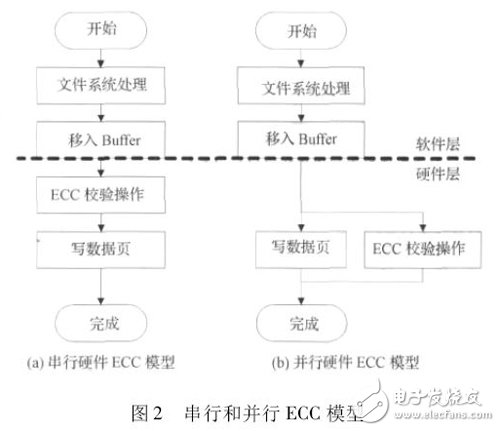

2. 2. 1 FPGA 逻辑结构

大容量固态存储器以FPGA 为控制核心,由多片NAND Flash 构成存储阵列,采用PCI 接口实现数据的高速传输。FPGA 作为大容量存储器的控制核心,主要有三大部分: PCI 核,NAND Flash 主控制器和ECC 功能模块,如图3 所示。采用Xilinx ISE 自带的PCI 核可以实现与CPU 端的通信和高速传输。NAND Flash 主控制器主要实现对NAND Flash 芯片的块擦除、页读取、页编程、ID 读取、状态查询和复位等命令的时序 *** 作。ECC 功能模块完成ECC 码生成,错误检测,上报校验信息等工作。

FPGA 逻辑设计不仅要考虑NAND Flash 芯片对于块擦除、页读取、页编程等 *** 作的时序要求和以页为单位进行读写访问的特点,还要保证ECC 功能模块能够正确地检错纠错。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)