现场可编程门阵列FPGA 常常进行大数据量的处理,数据的存储便成了问题,利用SPI Flash 大容量、读写速度快、成本低廉以及数据在断电后不丢失的特点,可以将配置数据存储于SPI Flash 中[1] 。它比起传统的并行总线接口Flash 来说节省了很多的I/ O 口资源,从而为系统功能的扩展提供了更多的可能。为此提出了一种基于FPGA 的SPI Flash 控制器的设计方法,并用Verilog HDL 实现,在Isim 中得出仿真和验证结果,最终应用在自行设计的VGA显示控制电路中得到成功应用,而且可以扩展到所有类似系统中[2] 。

1 系统总体方案设计FPGA 芯片采用的Spartan-6 系列的xc6slx9 芯片,封装采用tqg-144,该系列FPGA 能提供高达400MHz 的工作时钟,高达5 720 个高效的双寄存器6 输入查找表(LUT)和一系列丰富的内置系统级模块,采用成熟的45 nm 低功耗铜制程技术制造,实现了性价比与功耗的完美平衡。该芯片有9152 个逻辑单元(Logic Element),32 个18 kbyte 的Block RAM 模块,16 个18伊18 bit 嵌入式乘法器,2 个锁相环(PLL)和4个时钟管理模块(DCM)。在这款144 针tqg 封装的FPGA 中,用户可用I/ O 为102 个[3] ,可以满足本系统的需求。

Flash 芯片采用的配置芯片是Winbond 公司的W25Q80BV 系列8 M bit 容量的SPI Flash,该芯片共由16 部分组成,每一部分有256 页,每页有256 个字节。该系列芯片具有先进的写保护机制,读取数据的最大时钟速率为50 MHz。工作的电压范围为2.7 V ~3.6 V,具有整体擦除和扇区擦除、灵活的页编程指令和写保护功能,数据保存至少20 y(year),每个扇区可承受100 000 次擦写循环。SPI Flash 具有掉电保存能力,在系统上电时,FPGA 首先从配置芯片SPIFlash 中读取编程数据,并对FPGA 进行加载。SPIFlash 的HOLD#和WP#管脚要接上拉电阻, 因为FPGA 上电时管脚为高阻态,如无此上拉电阻,FLASH的HOLD#和WP#输入为浮置状态,没有确定的电平,进而导致数据总线电平也不确定,这是不允许的。

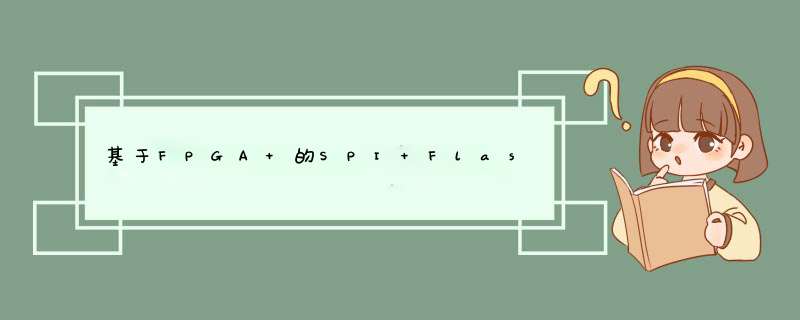

本系统由串口、FPGA 和SPI Flash 构成,系统整体框图如图1 所示。

图1 中,FPGA 为电路核心,一方面接收来自PC串口的数据,并将数据写入Flash 中;一方面从Flash中读出数据;另一方面产生系统所需的各种控制信号。作为现场可编程器件,FPGA 能方便地烧入程序来改变它的功能,所以在设计调试时,可将。 bit 文件烧入FPGA 进行在线调试,也可将。 mc文件程序直接下载到SPI Flash 中进行功能验证。

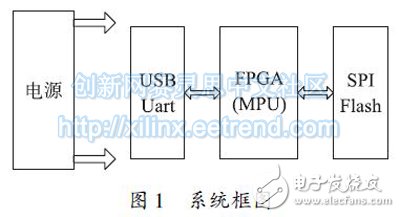

2 FPGA 内部模块设计FPGA 的顶层文件包括七个模块,如图2 所示。

图2 中,复位信号主要是同步外部的复位信号;DCM 模块主要是倍频和管理时钟;串口接收模块把从串口得到的数据缓存到FIFO;Flash 控制模块主要是控制对外部SPI Flash 的读写,把从串口得到的数据存入到SPI Flash,并不断把SPI Flash 中的数据送到串口发送模块;CoreRAM 是Xilinx 专用的一个IP 核,本设计中用于FPGA 内部数据的缓存;SPI 接口模块为SPI Flash 提供串行时钟,并实现数据的串并转换。当上层用户发送指令要将FPGA 的配置数据存入SPI Flash 时,配置数据从串口接收模块输出给Flash 模块, Flash 模块将数据不断提取到CoreRAM 中,CoreRAM 中的数据经过Flash 模块写入到SPI Flash 中。当系统重新上电要对FPGA 进行配置时,将SPI Flash 中的数据读入到Flash 模块中,再将Flash 模块中数据缓存在CoreRAM 中,最后将CoreRAM 中的数据提取给上层相应的模块,完成对FPGA 的配置。

从以上分析可以知道,FPGA 内部的数据流向非常的明朗,模块之间的关系也很确切,所以这个框图的划分具有一定的科学性。如果总体的框图没有划分好,调试成功的可能性也是非常小的。另外,在升级的时候如果要改变数据的获得方式,只要用新的程序替换串口接收模块即可;如果要改变数据的显示方式,只要用新的程序替换串口发送模块即可。下面分别介绍各功能模块的实现。

2. 1 串口接收和发送部分

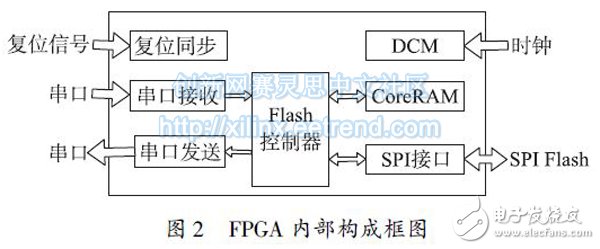

串口发送和接收部分相似,串口接收部分是将来自PC 的串口数据发送到Flash 控制器中,而串口发送部分是将从Flash 中读到的数据发送给PC 机,是串口接收的逆向过程,下面以串口发送部分为例进行分析。串口接收模块的框图如图3 所示。

图3 中包含3 个子模块,串口接收模块接收来自PC 串口的数据,为了使速度尽可能的快,设计用的波特率为115 200 bit/ s;缓存接口主要是把串口接收到的数据缓存到FIFO;FIFO 是例化的一个模块,用作数据缓存。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)