利用FPGA进行数字信号处理时,信号中的直流分量通常需要去除,而直流分量在AD前段就存在,如果采用模拟电路去除直流分量比较复杂,因此通常在AD后端数字域去除直流分量。在FPGA中,常规去直流的方法是先对信号进行累加,然后对累加值进行移位即可得到直流分量,如累加8192个数据,则直流分量可由累加值右移13位得到。

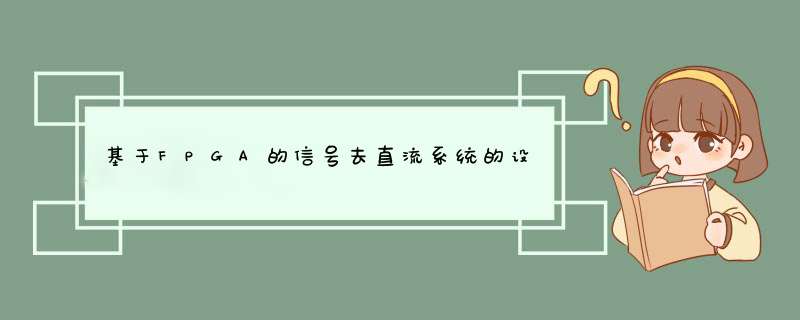

本文介绍一种根据Xilinx FPGA中DSP48E1资源设计的去直流模块,其基本原理采用一阶滤波器,如图1所示,通过一个一阶RC电路,在V0端可等效一个低通滤波器,得到直流分量。

图1

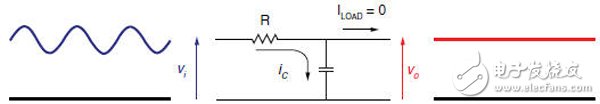

由上式可推导出,定义系数,由此可得到下式:

由上式可得到如图2所示结构:

图2

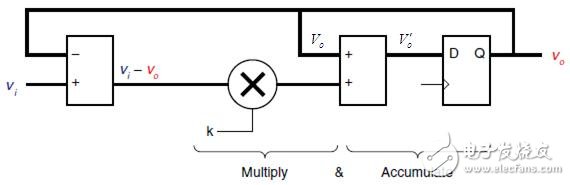

仔细观察发现图2中结构与Xilinx FPGA的DSP48E1结构十分相似,如图3所示,两个结构做了类比,其中Vi - Vo的减法可由DSP48E1中的Pre-Adder实现,k*(vi - vo)的乘法可由DSP48E1中的MulTIpler实现,而Vo + k*(vi - vo)加法可由DSP48E1中的Accumulator实现。因此实现这个去直流模块只需1个DSP48E1资源,并且在Xilinx 7系列FPGA中,DSP48E1最大支持25-bit的Pre-adder、25*18-bit的MulTIpler和48-bit的Accumulator,基本可满足常规处理。

图3

具体实现:

在ISE的HDL language template中可以找到DSP48的宏定义,这边需要用到ADDMACC_MACRO,只需要将这个宏模板拷贝到程序中直接例化即可调用DSP48,去直流模块的DSP48E1实现代码如下所示:

module DCOff_DSP(

input clk,

input rst,

input [15:0] din,

output [15:0] dc

);

wire signed [31:0] PRODUCT;

wire signed [15:0] K;

wire signed [31:0] ACOUT;

assign K=16'h0085;

ADDMACC_MACRO #(

.DEVICE("7SERIES"), // Target Device: "VIRTEX6", "SPARTAN6", "7SERIES"

.LATENCY(4), // Desired clock cycle latency, 0-4

.WIDTH_PREADD(16), // Pre-adder input width, 1-25

.WIDTH_MULTIPLIER(16), // MulTIplier input width, 1-18

.WIDTH_PRODUCT(32) // MACC output width, 1-48

) ADDMACC_MACRO_inst (

.PRODUCT(PRODUCT), // MACC result output, width defined by WIDTH_PRODUCT parameter

.CARRYIN(1'b0), // 1-bit carry-in input

.CLK(clk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.LOAD(1'b1), // 1-bit accumulator load input

.LOAD_DATA(PRODUCT), // Accumulator load data input, width defined by WIDTH_PRODUCT parameter

.MULTIPLIER(K), // Multiplier data input, width defined by WIDTH_MULTIPLIER parameter

.PREADD2(-PRODUCT[31:16]), // Preadder data input, width defined by WIDTH_PREADD parameter

.PREADD1(din), // Preadder data input, width defined by WIDTH_PREADD parameter

.RST(rst) // 1-bit active high synchronous reset

);

assign dc=PRODUCT[31:16];

endmodule

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)