根据SATAⅡ协议与SATAⅢ协议的不同,分别从物理层、链路层和传输层详细讨论了基于FPGA 的SATAⅢ协议的实现,成功实现了控制器与支持SATAⅢ协议的SSD 硬盘之间的通信。

随着硬盘技术的发展,硬盘容量变得越来越大,接口传输速率越来越快。但是,随着传输速率的提升,并行传输技术使得总线间的相互干扰越来越难以抑制,大幅上升的传输误码率导致经传输后的数据无法使用。当PATA 总线的速率达到133 MHz 的时候,并行传输技术已无法抑制串扰带来的误码,基于串行传输技术的SATA 孕育而生,其所采用的高速差分传输技术从根本上解决了因串扰导致的传输误码问题。与PATA 接口相比,SATA 接口优势明显,其使用的接口针脚少,体积小,传输速率快,稳定性好,可靠性高,抗干扰能力强。

2001 年, Intel、DELL、Seagate 等几大厂商组成了SerialATA 委员会,提出了第一代SATA 标准,以取代PATA。SATAⅠ的传输速率可达150 MBps,直接超越了当时传输速率最快的PATA。2005 年,SerialATA 委员会对SATAⅠ进行了改进,形成了第二代SATA 标准,SATAⅡ的传输速率为SATAⅠ的两倍,达到了300MBps。随后SSD 技术的飞速发展推动了串行传输技术的继续前行,第三代SATA 标准于2009 年诞生,其传输速率为SATAⅠ的四倍,达到了600 MBps,但还远远没有达到串行传输技术的极限。随着硬盘及计算机技术的发展,SATA 标准还将得以延续[1]。

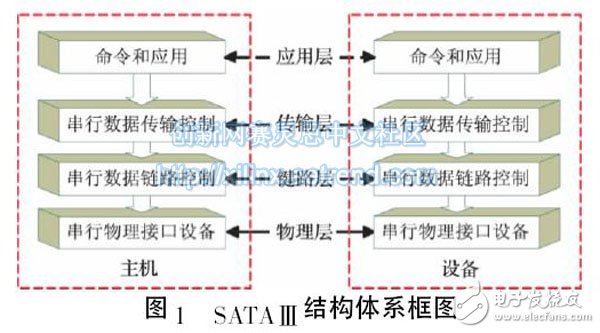

1 SATAⅢ协议的结构SATAⅢ协议的体系结构继承了以前的SATA 标准,分为物理层、链路层、传输层和应用层,其结构原理框图如图1 所示。

物理层实现高速串行信号的发送和接收,完成数据串并、并串转换以及编解码处理。链路层负责编码帧数据,校验数据,添加帧的边界和流量控制。链路层只发送和接收帧,并不需要知道帧的内容。传输层是整个SATA 协议的核心,负责把发送数据封装成FIS( Frame InformaTIon Structure) 帧格式,把接收到的FIS帧去除封装。应用层相当于人机交互界面,完成对SATA 控制器的各种 *** 作。

2 SATAⅢ控制器的设计实现2. 1 物理层设计

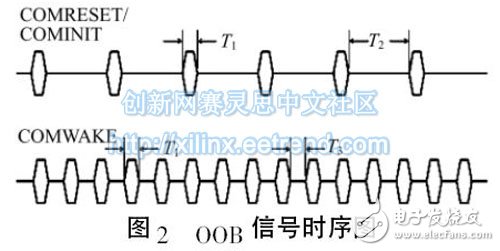

根据SATAⅢ协议规范,物理层主要实现主机与设备的初始化和串行数据流的传输。本设计采用了Xilinx 公司Virtex5 系列的XC5VFX70T。该FPGA 具有16 个GTX,每个GTX 的传输速率可达6. 5 Gbps。Virtex5 系列下的所有具有RockeTIO 的FPGA 均已完全支持SATA Ⅱ 协议,但虽然FX 系列FPGA 的RockeTIO 传输速率能达到6 Gbps,可仍不支持SATAⅢ协议规范[2]。本设计中物理层的重点是: 设计SATAⅢ协议的OOB( Out Of Band) 信号传输时序,以满足协议规范中的要求,从而实现链路双方的握手。3 个OOB 信号的时序图如图2 所示。

Gbps 的传输速率,可根据协议描述设计初始化状态机,控制GTX Core 中与OOB 相关的信号,即可完成主机与设备的初始化。但是,当RockeTIO 的传输时钟达到3 GHz 时( 即双沿6 Gbps 传输速率) ,图2 中T1和T3将由106. 7 ns 缩短为53.3 ns,而T2

也将由为320ns 缩短为160 ns。这样导致初始化数据段周期错误,无法完成主机与设备之间的初始化。

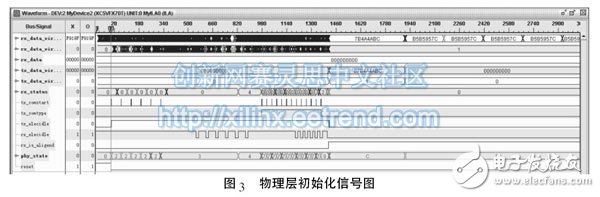

为了满足规范中OOB 信号的时序要求,本文中重新设计OOB 产生信号,通过手动控制OOB 信号的产生,按周期连续产生不少于6 个周期的OOB 信号。这样,虽然T1仍保持为53.3 ns,但T2和T3的时间间隔可以手动调节,本设计中将其分别扩展为373.3 ns 和160 ns,以保证空闲段周期的正确性,从而完成主机与设备的正常初始化。图3 为chipscope 抓取的物理层初始化信号图。

以上方法通过增加T2和T3的时长来保持OOB信号的周期恒定不变,以满足SATAⅢ协议规范中的定义。考虑到OOB 信号的数据容差较大,本文也实验了保持T3为106.7 ns、T2为320 ns、T1为53.3 ns 的情况,即缩短数据段周期、保持空闲时间的情况。在这种情况下,FPGA 无法完成SATA 协议的初始化,不能与硬盘建立通信连接。

2. 2 链路层设计

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)