针对传统的FIR 滤波器的缺点,介绍了一种基于FPGA 乘法器的FIR 滤波器设计方法,该滤波器利用FPGA 自带的18位乘法器MULT18 × 18SIO 进行乘法计算,利用寄存器对相乘结果进行累加,实现了FIR 滤波功能。该滤波器具有占用极少的资源、提高滤波速度和高速灵活性等优点。

在通信系统、航空航天系统、雷达系统、遥感遥测系统等工程技术领域,无论是在信号的获取、传输,还是信号的处理和转换都离不开滤波技术。由于FIR 滤波器具有严格的线性相位和在系统中具有稳定性,因此FIR 滤波技术具有广泛的应用[1-4]。

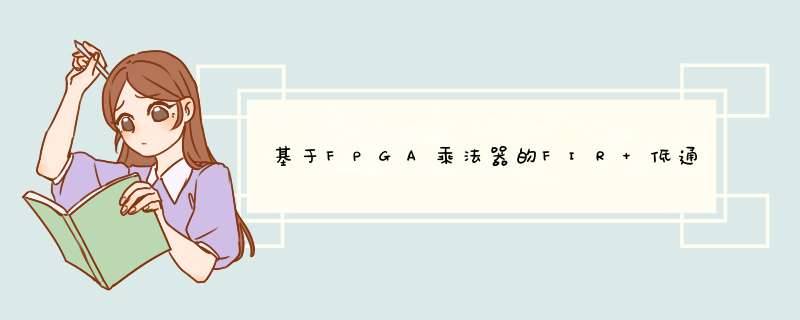

1 FIR 低通滤波器整体设计本文主要介绍的是FIR 低通滤波器,该FIR 低通滤波器主要由硬件电路和FPGA 程序组成。FIR 滤波器硬件电路主要由信号调理电路、AD 转换电路、FPGA 控制电路、FT245RL 电路和上位机组成,其中FPGA 内部程序模块包括AD 采集控制模块、FIR 滤波器采样模块、MULT 18 ×18SIO 乘法器模块、累加模块、36 位数据拆分模块、FIFO模块和FT245 控制模块。该滤波器主要功能是利用信号发生器产生特定频率的正弦波,通过信号调理电路进行调理后经过12 位的AD 转换器进行转换输出数字信号,FIR 滤波器采样模块工作在60 MHz 的时钟内,并且以10 kHz 的采样率对AD 输出的数字信号进行采样,采样到的数字信号值连同FIR 滤波系数输出到18 位乘法器模块,经过乘法运算后进行累加,累加出来的是36 位数据,最终通过FT245 组成的USB 接口传给上位机进行曲线显示,所得结果即为滤波后的数据,系统组成原理如图1 所示。

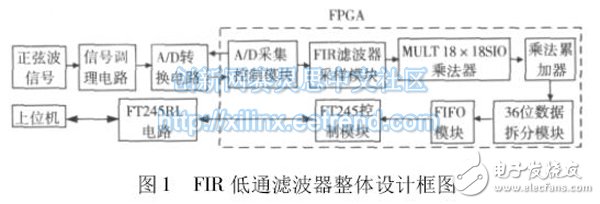

2. 1 AD 转换器电路

本系统中对于输入电压的采样率为10 kHz,因此采用了AD 公司的高性能逐次逼近型A/D 转换芯片AD7492BRU-5,最大转换速率为1. 25 ×10 次/s ,具有12位的并行数据输出接口,并且具有三态功能,能够满足系统采样要求。

由于AD7492BRU-5 的基准电压为2. 5 V,而输入的模拟信号范围为0 ~5 V,因此在模拟信号进入AD 转换器之前还需要对信号进行适当的调理,调理电路如图2 所示。采用两个10 kΩ 电阻对输出的模拟信号进行分压,使其范围满足A/D 转换器的输入要求,并通过电压跟随器进行输出,信号不会失真。

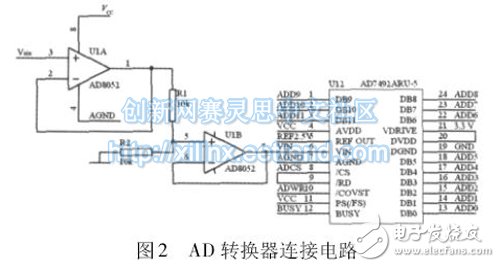

2. 2 FT245 接口电路

本系统中FPGA 发送的滤波数据通过USB 接口回传给上位机,上位机读取USB 的数据,并对数据进行存盘。USB 接口电路采用FTDI 公司的FT245RL 作为USB 接口芯片实现上位机与FPGA 的数据通信。FT245RL 无需编写固件程序,可以使用FTDI 公司提供的驱动程序,并且兼容USB1. 1 及USB2. 0 协议。USB 连接电路如图3 所示,该电路中数据传输线接一个共模电感ACM-2012-900,当传输差分信号USBDM 和USBDP 上有共模干扰时,由于共模信号产生磁场叠加,在共模电感上形成高阻抗,从而达到滤除共模干扰的目的。USB 口接地端接一个磁珠,这样连接可以更好地防止电源不稳对数据传输的干扰。USB 接口从FPGA 读取数据,FPGA 内部只要判断到FIFO 中产生半满信号,就将数据传输到USB 接口,最终利用上位机进行读取。

本设计采用Xilinx 公司XC3S400 的FPGA 进行程序验证,XC3S400 是高密度的可编程逻辑器件。它的主要特点包括具有最小5 ns 的引脚到引脚的逻辑时延,全局时钟最高引脚最高输入频率为66 MHz,内核用1. 2 V 供电,I /O 口可设置在3. 3 V 工作。该器件具有丰富逻辑的资源,包括16 个MULT18 × 18SIO,可以进行大量的乘法运算[8]。

FIR 滤波器程序主要由采样模块、乘法器模块、累加和模块组成,采样模块功能是采集60 个采样值、并把滤波系数输出到乘法器与采样值进行相乘。乘法器模块主要功能是对60 个采样值和60 个滤波系数进行相乘,所得的相乘结果输入累加器。累加器就是将输入的60 个结果进行累加,得到36 位的滤波结果[9-10]。

3. 1 采样模块

采样模块主要是对AD 转换后输出的值进行采样,本设计中采样率为10 kHz,也就是AD 的采样率为10 kHz,而滤波器对AD 转换后输出的值的采样率也是10 kHz,它们的实现在程序上是同步的。在AD 输出模块当中,每当数据转换完成输出时,会产生一个rdy 上升沿信号,采样模块接收并辨别rdy 上升沿信号后接收第一个数据,并把第一个滤波系数输出到MULT18 × 18SIO 乘法器,同时给乘法器CLK 端产生一个上升沿信号,启动乘法器进行相乘,相乘结果时间极短,所以可以实现高速相乘运算。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)