在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,而要减轻反射信号的负面影响,有三种方式:

1)降低系统频率从而加大信号的上升与下降时间,使信号在加到传输线上前,前一个信号的反射达到稳定;

2)缩短PCB走线长度使反射在最短时间内达到稳定;

3)采用阻抗匹配方案消除反射;

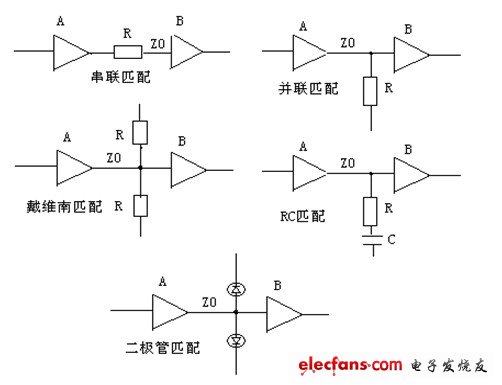

在高速系统设计中,第1种是不可能的,而第2种也是不实际的,通常要缩短PCB布线长度,可能需要增加布线层数、增加过孔数,从而得不偿失,那么第3种是最好的方法,常用的阻匹配方式有以下几种:

1.源端串联匹配

源端串联匹配就是在输出BUFFER上串接一个电阻,使BUFFER的输出阻抗与传输线阻抗一致;此电阻在PCB设计时应尽量靠近输出BUFFER放置 ,常用的值为:33殴姆。

对于TTL或CMOS驱动,信号在逻辑高及低状态时均具有不同的输出阻抗,而一些负载器件可能具有不同的输入输出阻抗,不能简单的得知,所以在使用串联端接匹配时,在具有输入输出阻抗不一致的条件下,可能不是最佳的选择;在布线终端上存在集总线型负载或单一元件时,串联匹配是最佳的选择;

串联电阻的大小由下式决定:

R=ZO-R0 ZO--传输线阻抗 R0--BUFFER输出阻抗

串联匹配的优点:提供较慢的上升时间,减少反系量,产生更小的EMI,从而降低过冲,增加信号的传输质量;

串联匹配的缺点:当TTL/CMOS出现在同一网络上时,在驱动分布负载时,通常不能使用串联匹配方式。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)