本实例通过Verilog编程实现在红色飓风II代Xilinx开发板上面实现对键盘、LCD、RS-232等接口或者器件进行控制,将有键盘输入的数据在LCD上面显示出来,或者通过RS-232在PC机上的超级终端上显示出来。

2.实例目标通过本实例,读者应达到下面的目标。

了解PS/2接口协议。

掌握键盘的工作原理。

编写Verilog程序实现通过开发板上PS/2接口读取键盘的输入信息。

原理简介

PS/2键盘履行一种双向同步串行协议。换句话说每次数据线上发送一位数据,并且每在时钟线上发一个脉冲就被读入,键盘可以发送数据到主机,而主机也可以发送数据到设备。但主机总是在总线上有优先权,它可以在任何时候抑制来自于键盘的通信,只要把时钟拉低即可。

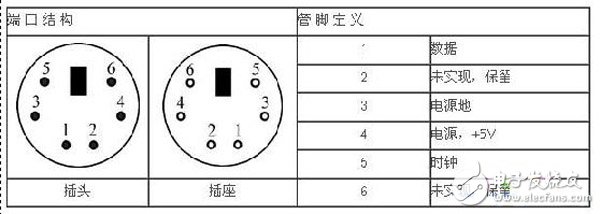

本实例要编写一个能实现PS/2端口功能的Verilog程序。首先我们要了解PS/2端口的结构与管脚功能定义,如表1所示。

表1 PS/2端口结构及管脚定义

可以看到,PS/2里面只有一个数据口,若要分辨很多按键就需要一个高效率的分辨方法。键盘的处理器花费很多的时间来扫描或监视按键矩阵。如果它发现有键被按下,释放或按住键盘,将发送扫描码的信息包到计算机。

扫描码有两种不同的类型:“通码”和“断码”。当一个键被按下或按住就发送“通码”,当一个键被释放就发送“断码”。每个按键被分配了惟一的“通码”和“断码”。这样,主机通过查找惟一的扫描码就可以测定是哪个按键。

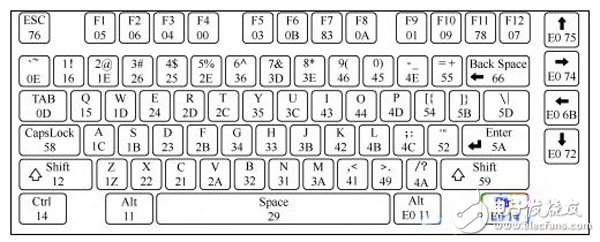

每个键一整套的通断码组成了扫描码集,图1中包含了键盘上面大部分按键的扫描码。

当按键被释放以后,键盘回在扫描码前面加上一个“F0”作为按键松开信号。同时有的按键是Extended(扩展)键,此时要在它们的扫描码前面加上一个“E0”作为开头,这种按键松开以后将在扫描码前面附加上“E0F0”。

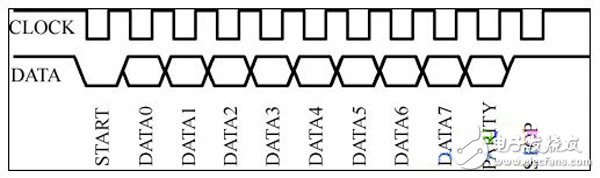

下面我们来了解信号是如何从键盘输入通过PS/2端口的数据线输入的。首先键盘要检测数据线和时钟线是否都为高,只有它们都处在高的状态才可以写数据。从键盘发送到主机的数据在时钟信号的下降沿(当时钟从高变到低)的时候被读取。

键盘主要使用一种每帧包含11位的串行协议:第一位是起始位,始终为“0”;接下来是8位数据位,排列顺序是由低到高;再后面是奇偶校验位;最后是结束位,始终为“1”。如图2所示为该协议的时序图。

图1 键盘扫描码

图2 键盘串行协议

实例详解

此处仅给出主要的 *** 作流程。

(1)启动ISE软件。

(2)创建新工程。

(3)编写键盘串行协议。

按照图2的时序编写相应的Verilog代码,具体源代码参见实例代码。

(4)添加设计输入。

将编写好的接口协议加载至工程中,完成接口控制与系统的对接。

(5)设置器件及管脚约束。

按照开发板的说明进行相关的设置。

(6)下载验证。

下载程序后,将键盘接至开发板上,通过开发板的LCD可以看到键盘输入的字符。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)