为设计寻找“完美”FPGA 的重要性日渐升级,其中功耗已成为主要考虑因素。功耗管理在大部分应用中都非常关键。某些标准已为单卡或者单个系统设定了功耗上限。鉴于此,设计人员必须在设计过程中更早地对功耗问题加以考虑,一般来说应该从选择 FPGA 开始。

减少 FPGA 的功耗可以降低供电电压,简化电源设计和散热管理,降低对电源分配面的要求,从而简化电路板设计。低功耗还可以延长电池寿命,提高系统的可靠性(运行温度较低的系统寿命更长)。

功耗挑战

鉴于这些问题的存在,设计人员必须在设计过程中尽早对电源和热管理问题有更加清楚的认识。给器件加上散热器并不足以解决这些问题。因此设计人员必须尽量减少设计中的逻辑用量。

首先来看几点指南,有助于理解在设计过程各个阶段应采取何种措施来降低FPGA的功耗。很明显,在设计过程的初期彻底理解这些问题能带来最大的收益。

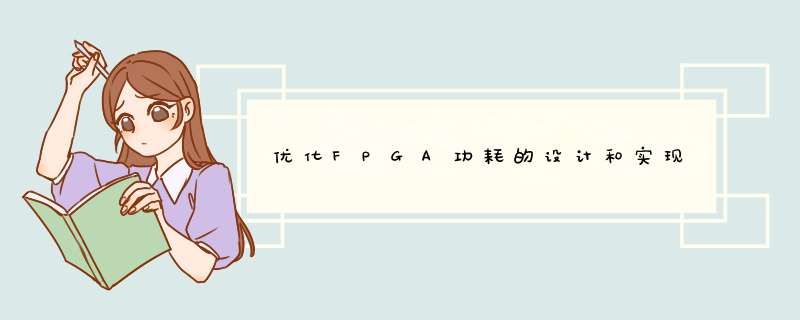

图 1 说明了包括 FPGA 选择以及低功耗设计技巧在内的贯穿整个设计过程的不同设计点

7 系列工艺技术

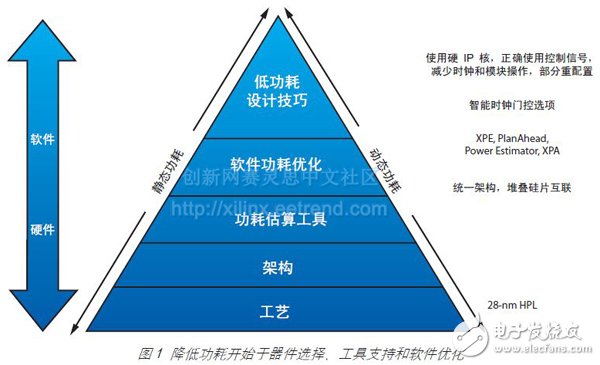

在选择 FPGA 的过程中, 应谨慎考虑工艺技术,它能帮助用户判断器件的漏电流和性能。赛灵思 7 系列FPGA 采用 28 HPL (28nm 高性能低功耗)工艺,在提高性能的同时可显著降低功耗(见第 41 期《赛灵思中国通讯》的封面故事)。选择采用低漏电流的 HPL 工艺制造的器件,可以避免在FPGA 设计中使用复杂且成本高昂的静态功耗管理方案。

尽管 28 HP 工艺 FPGA 的性能并没有超越 7 系列的其它 FPGA,但其静态功耗还不到竞争对手 FPGA 静态功耗的一半,而且不会造成严重的漏电流问题。图 2 显示了 7 系列产品的全面降耗情况,整体功耗仅为上一代40nmFPGA 器件的一半。

设计人员可以在开发阶段选择较大的 FPGA,然后在生产过程中选择较小的 FPGA。选择较小的 FPGA 不仅可以降低成本,还能降低系统功耗。

所有 7 系列 FPGA 均采用统一的架构。这种统一架构便于在赛灵思 7 系列的不同 FPGA 器件之间方便地进行向上或向下迁移。如果需要从 Virtex®-6 或者 Spartan®-6 器件迁移至7 系列器件或者在 7 系列器件之间迁移,请参阅“7系列用户指南”(UG429)。

赛灵思堆叠硅片互联技术

对较大的系统来说,设计人员一般会选择多个 FPGA。这种架构往往需要在各个 FPGA 之间高速传输数据,这是一项复杂、困难的工作。选择采用赛灵思堆叠硅片互联技术制造的大型 7 系列 FPGA,比如 XC7V1500T 和XC7V2000T 器件,就可以避免这个问题。简单地说,堆叠硅片互联技术就是将多片芯片布置在具有成千上万连接关系的插入式结构中,用以制造统一的大型器件。堆叠硅片互联技术的优势之一在于,与采用标准单片电路的类似尺寸的器件相比,可显著降低静态功耗。

堆叠硅片互联技术 (SSI) 还能大幅度降低 I/O 互联功耗。与在电路板上布置多块 FPGA 的方法相比,SSI 技术有很大的优势,其 I/O 互联功耗比采用 I/O 和收发器构建的等效接口低 100 倍(带宽/W)。功耗大幅下降是因为所有连接都构建在芯片上,无需功耗将信号驱动到片外,这样可实现难以置信的高速度和低功耗。

电压扩展增强选项

赛灵思 7 系列 FPGA 提供重要的电压扩展选项。

7 系列 FPGA 为 -3L 和 -2L 器件提供扩展 (E) 温度范围(0-100 摄氏度)。由于 28 HPL 工艺提供的余量,-2LE 器件可在 1v 或 0.9v 下运行。这些器件被分别命名为 -2L (1.0V) 和 -2L(0.9V)。运行在 1.0V 下的 -2L 器件的速度性能与 -2I 和 -2C 器件相当,但静态功耗显著降低。运行在 0.9V 的 -2L 器件性能与 -1I和 -1C 器件相似,但静态和动态功耗都有所下降。

仅仅将这些器件的电压降低到0.9V 就可降低静态功耗约 30%。降低电压也会降低性能,但赛灵思根据速度和更加严格的漏电流规格对这些 -2L(0.9V) 器件进行筛选。这种筛选方法能够使器件在最劣工艺条件下的功耗比标准速度等级器件的功耗降低 55%。

选择 -2L 器件,用户还能进一步降低动态功耗。由于动态功耗与 VCCINT2成正比,VCCINT下降 10% 可带来功耗20% 的降幅。

功耗估算工具

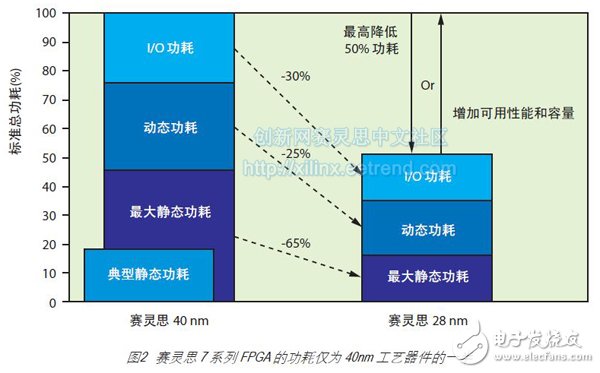

今天的市场上有丰富的工具可供设计人员选择,用以在整个开发过程中评估 FPGA 设计的散热和电源要求。图 3是FPGA 开发过程中每个阶段可供使用的赛灵思工具。

为降低功耗,用户必须尽一切可能减少设计中使用的逻辑数量。首先是使用专用的硬件模块,而不是在 CLB 中实现相同的逻辑。

在设计初期,XPower EsTImator(XPE) 电子数据表能够在初步设计和实施之前对功耗进行早期估测。XPE 可用于架构评估和器件选择,帮助确定应用所需的合适的电源和散热管理组件。

PlanAheadTM 软件则用于估测设计电源在 RTL 级的分配情况。设计人员可以使用约束条件或者 GUI 来设定器件的运行环境、I/O 属性和默认活跃度。PlanAhead 软件随即读取 HDL 代码,估算所需的设计资源,并对每种资源的运行状态进行统计分析,得出功耗估算报告。由于能够掌握有关设计意图的更加详细的信息,因此 RTL功耗估计器的准确性优于 XPE 电子数据表,但不及Xpower Analyzer 得出的后期布局布线分析结果准确。

Xpower Analyzer (XPA) 是一种专门用于分析布局布线设计功耗的工具。它采用全面综合的GUI,可以对特定运行条件下的功耗和发热量信息进行详尽的分析。

用户可以在两种不同视图间切换,用以确认各种类型模块(时钟树、逻辑、信号、IO 模块、 BRAM 等硬 IP核或 DSP 模块)的功耗或设计层级功耗。两种视图都能让用户进行详细的功耗分析。并为确定设计中最耗电的模块或部件提供了一种非常有效的方法,从而简化了功耗优化工作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)