利用赛灵思Spartan-6器件和一些外设组件轻松为学生和新手构建一款有趣的演示平台。

我们近期打算北京理工大学开发一款数字设计教学平台,它能展现FPGA在通信和信号处理领域的实际效用。这个平台要直观易用,能帮助学生了解数字设计的各个方面,同时还要便于学生针对自己独特的系统设计进行定制。

系统架构

我们几乎完全用FPGA来构建XRadio平台,省略了放大器或分立滤波器等传统模拟组件的使用(如图1所示)。首先,我们将用电线连接成的简单耦合电路链接至FPGA的I/O引脚,创建出基本天线。该天线用于发射RF信号到FPGA,FPGA通过数字下变频和频率解调实现FM接收器的信号处理。我们随后通过I/O引脚向耳机输出音频信号。我们添加机械旋转增量解码器来控制XRadio的调频和音量。我们设计该系统可让调频和音量信息显示在7段LED模块上。

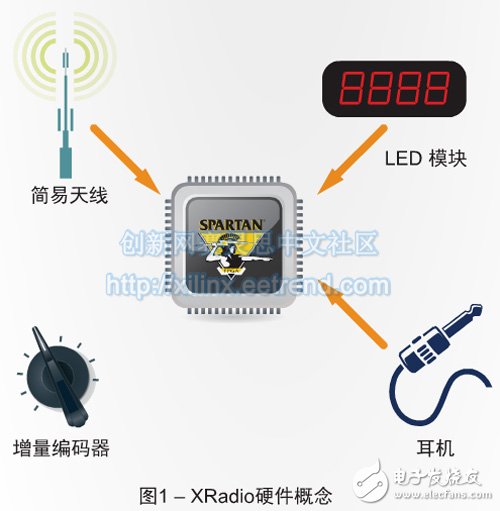

图2显示了FPGA的顶层逻辑方框图。在这个设计中,耦合到FPGA输入缓冲器的RF信号量化为1位数字信号。量化的信号乘以数控震荡器(NCO)生成的本地震荡信号,倍频后的信号经滤波可得到正交IQ(同相正交)基带信号。它随后通过频率解调器和低通滤波器从IQ信号获得音频数据流。

实现细节

我们要解决的第一大难题就是如何将天线接收到的信号耦合到FPGA。在首次试验性设计中,我们将FPGA I/O配置为标准单端I/O,然后我们用电阻R1和R2构建分压器,以在FPGA引脚处的VIH和VIL之间生成偏置电压。天线接收的信号可通过耦合电容C1来驱动输入缓冲器。由内部240MHz时钟驱动的D触发器的两级负责对该信号进行采样。触发器输出端获得等间隔的1位采样数据流。

数据流随后进入脉宽调制(PWM)模块,在其输出端上生成脉冲信号。脉冲信号经过滤波,可得到驱动耳机的比例模拟值。我们将控制器模块连接到机械旋转增量编码器和LED。该模块从增量编码器获得脉冲信号,以调节NCO的输出频率以及PWM模块控制的音频音量。

为了测试这个电路,我们将结果馈送给另一个FPGA引脚并用频谱分析仪进行测量,看看FPGA是否能准确接收信号。不过,它工作得并不好,因为分析器显示Spartan-6 FPGA的输入缓冲器有一个较小的120毫伏磁滞电压。虽然磁滞一般来说有利于避免噪声,但在本应用中我们并不希望有磁滞。我们必须想办法提高信号强度。

该设计大幅降低了信噪比,这是因为1位采样生成的噪声量化的结果。不过4个台在背景噪声下仍能正常收到。因此我们能证明这样一个理论,那就是FPGA的I/O引脚能用作比较器或XRadio中的1位模数转换器。

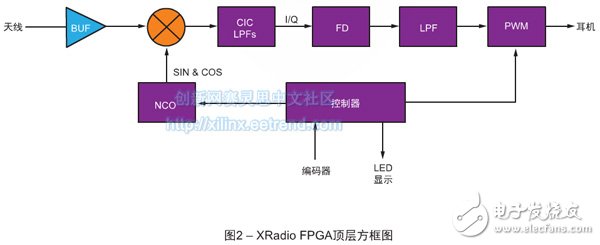

为了解决这一问题,我们发现差分输入缓冲器(IBUFDS)原语在正负终端之间灵敏度极高。我们的测试显示低至1 mV的峰至峰差分电压足以让IBUFDS在0和1之间摆动。图3显示了所设计的输入电路。在本实现方案中,电阻R1、R2和R3在IBUFDS的终端P和终端N处生成普通电压。接收到的信号通过耦合电容C1馈送给终端P(sidefile:///app/ds/)。AC信号经N侧的C2电容滤波后,其可用作AC基准信号。就此电路而言,FPGA将FM广播信号成功转换为1位数据流。

无线电能收到强度不同的大约7个FM频道,包括103.9MHz北京交通台。该设计大幅降低了信噪比,这是因为1位采样生成的噪声量化的结果。不过4个台在背景噪声下仍能正常收到。因此我们能证明这样一个理论,那就是FPGA的I/O引脚能有效用作比较器或XRadio中的1位模数转换器。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)