摘要:为了能够灵活地验证和实现自主设计的基于NoC的多核处理器,缩短NoC多核处理器的设计周期,提出了设计集成4片Virtex-6—550T FPGA的NoC多核处理器原型芯片设计/验证平台。分析和评估了NoC多核处理器的规模以及对FPGA硬件资源的需求,在此基础上给出了集成4片FPGA的开发板详细设计方案,并对各主要模块如互联架构、电源、板级时钟分布、接口技术、存储资源等关键设计要点进行阐述。描述了开发板各个主要模块的测试过程和结果,表明了该设计的可行性。

0 引 言由于基于传统SoC (system-on-chip)的单芯片处理器在内核频率、片上通信、功耗以及面积等方面面临着很大问题,基于NoC (network-on-chip)的多核处理器应运而生,从体系架构上解决了前者所面临的诸多问题。NoC互连结构具有IP间的并行通信、扩展性好以及吞吐量大等优势,并且解决了多核处理器的体系结构问题以及困扰总线结构的全局时钟问题。因此,NoC互连结构是多核处理器系统最有前途的解决方案。

目前,FPGA芯片作为承载和验证基于NoC的多核处理器硬件设计的途径,已经成为了研究热点,但是随着硬件设计的规模不断增加,单片FGPA的硬件资源并不能满足基于NoC的多核处理器需求。因此,本文设计的验证平台采用了4片Xilinx公司的40nm Virtex-6系列中的XC6VLX550T (FF1759);该芯片具有将近50万的逻辑单元、840个最大可用I/0、内部信号可达600MHz、36组2.5Gbps高速吉比特收发器端口以及丰富的分布式RAM、Block ft 。由此观之,集成4片该型号FPGA芯片的开发板能够为FPGA硬件设计人员提供足够多硬件资源,以便验证和实现基于NoC的多核处理器的原型芯片设计,也为以后在片上网络(NoO 上研究多核并行计算提供了条件。

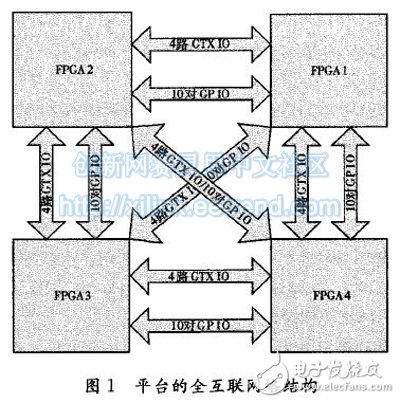

1 多FPGA开发板设计的总体方案 1.1 多FPGA的互联结构该开发板总体架构如图1所示,平台上有4片Xilinx XC6VLX550T FPGA芯片,因此可以将需要处理的任务划分多个子任务分配到不同FPGA芯片上的处理单元分别处理,从而实现任务处理的并行化;其任务间数据通信速度和同步时间等不仅取决于处理单元本身的通信速度,还取决于链接处理单元的通信互联网络。所以本平台的4片芯片利用FPGA提供的全双工差分高速GTX接口(low-voltage diferenTIal signaling,LVDS)_6]和单端模式的高速普通GPIOE ,实现片间的全互联网络结构;其中差分高速GTX接口的数据通信遵循Aurora协议,实现FPGA间的大量数据的高速传输,而单端模式的高速GPIO为FPGA开发人员提供自定义接口空间。

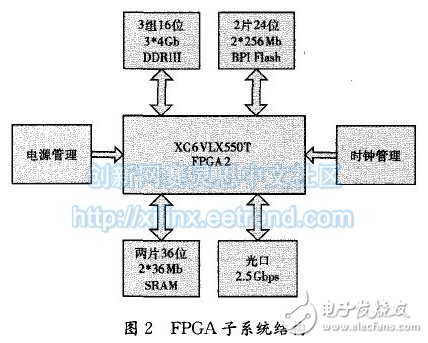

该开发板的具体实现如下:3大组GTX 10 (每组GTX IO由4路独立的GTX IO通道构成)分别与另外3块FPGA芯片的对应GTX IO相连,提供64位宽,125MHz的数据传输通道,实现4块FPGA芯片的全互联,片间吞吐率达lOGbps;以及1O对单端模式的高速GPIO。每片FPGA子系统包如图2所示,含如下模块:电源管理模块、独立的存储系统、板级时钟管理模块、FPGA的配置方式以及对外对内的接口模块。该开发板具有以下特点:

(1)丰富的逻辑资源,4片FPGA 总逻辑资源:549888*4= 2199552。

(2)丰富的存储资源,24片DDR3共计48Gb,片外SRAM达到256Mb,片内RAM共计115.8Mb。

(3)存储端口吞吐率大:DDRIII 400MHz*16*12=76.8Gbps,片外SRAM 167 MHz*64*4= 42.752Gbps。

(4)FPGA设计灵活性、通用性强:可以采用不同的处理器,也可以采用相同的处理器,如ARM等。

(5)仿真综合软件支持好:第三方的Modelsim能很好地完成功能仿真,而Xilinx公司的ISE则能很好地完成综合。

为了能够承载更多的硬件设计,开发板在设计中使用了4片FPGA为处理核心。因此,系统的功耗要远远超出普通系统的设计要求。所以,能否设计出满足系统功耗需求的稳压电源成为系统能否正常运行的关键。通常,电源设计有两种实现方式:低压差线性稳压电源LIX)与开关电源(DC_DC)开关电源(DC-DC)。u)O的特点是电源精度高、噪声小,比较适合于精密电路供电,其缺点是输出功率往往不够大,并且功率的转换效率偏低[8]。I)C-DC的特点是功率转换效率高,能够提供较大的电源功率,但相比较LIND而言其电源噪声会有所提高,因此I)C-DC一般作为系统整体稳压电源使用或直接为大功率器件供电。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)