可编程片上系统( SoPC)是在可编程逻辑器件的基础上发展起来的一种灵活、高效的嵌入式系统设计解决方案,系统设计者可以从传统的板级系统设计转换到芯片级系统设计,将系统设计中所需要的各个功能单元以IP ( Intellectual Property)的形式集成到FPGA中,实现集成度更高的嵌入式系统。

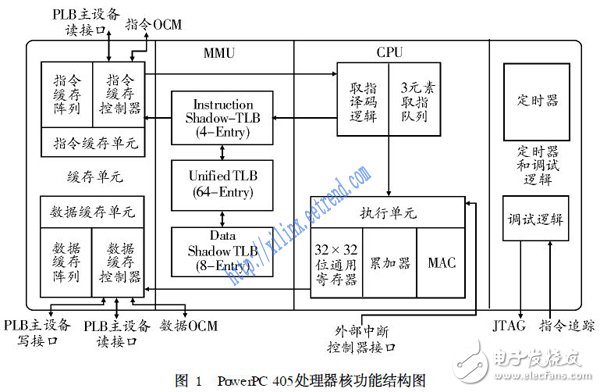

1 Virtex-4 FX系列FPGA介绍Virtex-4 FX系列FPGA芯片内至少包含一个PowerPC405处理器核,其功能结构如图1所示,该处理器核为32位哈佛结构的R ISC硬核,最高工作频率为400MHz。PowerPC405处理器包括以下功能单元: ( 1)5级数据通道流水线,包括取指、译码、执行、写回、装入写回5 级流水段; ( 2 ) 一个虚拟内存管理单元(MMU) ,支持可变页面大小和写保护、控制访问选项;(3)独立的指令Cache和数据Cache; ( 4)支持调试和跟踪,包含一个JTAG接口; ( 5)三个可编程计时器。另外, PowerPC 405硬核还具有如下特点: ( 1)支持硬件乘法和除法; ( 2) 32个32位通用寄存器; ( 3) 16KB两路组相联方式指令缓存( set-associaTIve) ; (4) 16KB两路组相联方式数据缓存、写回/写直达; ( 5 ) 实现PowerPC用户指令集架构(U ISA) ; ( 6)专用的片上存储器接口(OCM) ; ( 7 )支持IBM CoreConnect总线架构。

CoreConnect总线架构是由IBM开发的一种片上总线通信连接技术。CoreConnect总线包括处理器局部总线( PLB) 、片上外设总线(OPB)和设备控制寄存器总线(DCR) 。PLB总线为主设备和从设备之间提供高带宽、低延迟的连接,OPB总线为连接具有不同总线宽度和时序要求的外设提供了一条途径,减少了对PLB性能的影响,DCR总线用来控制PowerPC405处理器中的通用寄存器和设备寄存器之间的数据传输。

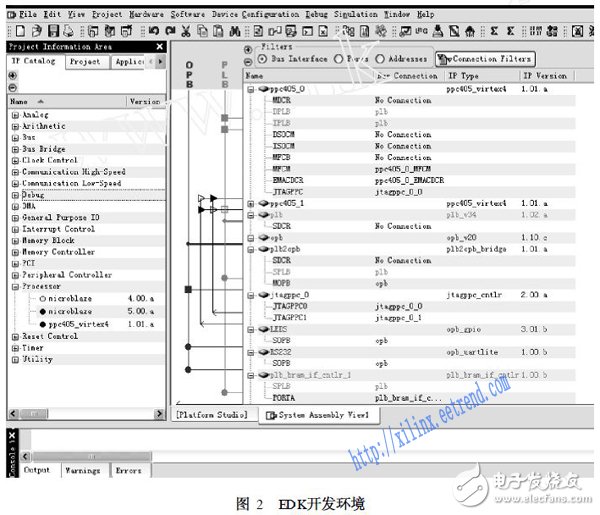

2 基于SoPC的嵌入式系统设计技术 2. 1 平台技术在平台的基础上来构建嵌入式系统为设计者提供了极大的便利, Xilinx 推出的嵌入式开发工具包( EDK)集成了诸如硬件平台产生器(platgen) 、硬件仿真模型产生器( SimGen) 、软件平台产生器( libgen) 、应用软件编译工具(GNU Compiler) 、软件调试工具(GNU Debugger) 等一系列工具。设计者可以通过集成在EDK环境下的Xilinx平台工作室(XPS)方便的调用各种工具进行基于SoPC的嵌入式系统设计。EDK环境下为系统设计者提供了丰富的IP资源,可利用现有的资源迅速搭建自己的嵌入式系统,完成整个PowerPC系统硬件的开发。如果开发工具包提供的IP库不能满足系统设计者的需求,设计者也可定制自己的IP。图2所示为EDK开发环境图形界面。

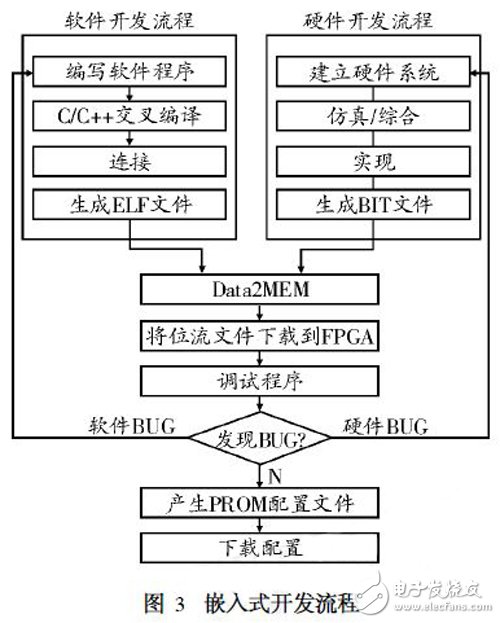

EDK环境为其自带的IP提供了相应的驱动程序及相关的函数,设计者可以通过调用这些函数加快应用程序的开发。对于设计者自行研制的IP,则需要编写相应的驱动程序。应用程序编写完成后,调用EDK下的GNU工具,编译连接生成可执行文件,再将硬件、软件文件结合在一起,产生可下载的位流文件下载到FPGA,使用Xilinx 微处理器调试工具(XMD ) 连接GNU调试工具进行应用程序调试,在确认应用程序正确无误,能实现系统功能之后,即可将位流文件转换成PROM的配置文件(MCS文件) 下载到目标板上的PROM,从而完成整个设计开发。图3为利用EDK工具进行嵌入式系统开发的流程。

基于SoPC的嵌入式系统设计过程中,系统设计者首先要明确设计需求,这对于整个设计具有指导性作用,也是将来设计完成后检验设计是否可用的标准之一。系统设计者根据设计需求来确定其系统架构,定义系统主要模块组成,决定其接口类型、总线结构、硬件功能及软件功能,完备的系统架构定义要能满足基本的设计需求,并能最大限度的提高系统整体性能。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)