随着计算机技术和图像处理技术的飞速发展,被动式电视跟踪系统以其高分辨率、直观感强、抗干扰性能好、成本低等优点,在军事上受到普遍重视,尤其在防空火控系统中获得了广泛应用。然而,由于数字图像处理技术数据量庞大,算法复杂,使得运算速度和精度往往成为限制电视跟踪系统整体性能的瓶颈。解决办法包括采用多处理器模式、提高核心处理芯片的运算能力或者探索更加高效的跟踪算法等。无论从设计的简化还是便于系统升级来说,提高核心处理芯片运算能力的方法无疑受到广大用户的青睐。专门用于视频图像或者音频信号的DSP (数字信号处理器)芯片能够满足以上需求。另外,FPGA (现场可编程门阵列)的诸多优点使其迅速应用到数字电路设计中。在核心芯片DSP的控制下,配合FPGA,能实现较复杂的图像处理任务和控制算法。FPGA对DSP起到重要的辅助作用,简化了电路设计,降低了成本,提高了稳定性。基于DSP的电视跟踪系统中,探索出了一种利用FPGA完成视频叠加和其他辅助功能的方法,构成了一个功能完整的实时目标搜索跟踪系统。

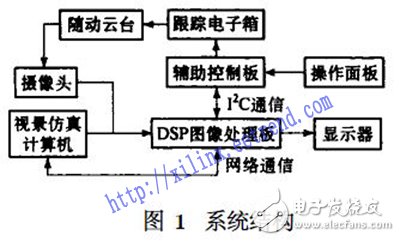

1 系统硬件设计系统组成框图如图1所示,主要由图像输入部分、图像识别处理部分和伺服随动系统三大部分组成。图像输入部分为摄像头或视景仿真计算机。摄像头用来摄取实时图像,视景仿真计算机则可以根据训练或评估的需要,设定多种目标模型和航路参数,利用3D建模软件模拟实战环境和飞行条件,实时产生视频图像信号。图像识别处理部分主要由图像采集模块、目标跟踪和识别模块、通信控制模块、伺服控制模块、字符和信息叠加模块、电源模块组成。实时采集并处理输入的视频信号,完成对目标的搜索和跟踪,并在输出视频上叠加字符、波门等信息。并将目标偏移量进行D/A转换及放大调整,监测 *** 作面板各个开关的状态。伺服随动系统根据上述偏移量对云台(摄像头)位置进行调整或将误差信号传输给视景仿真计算机,控制目标的生成,从而实现对仿真目标的电视跟踪。

本系统采用的核心处理芯片是TMS320DM642 DSP,这是一款针对视频/图像处理的定点DSP,其显著特征是高度集成了视频输入输出端口,支持所有主要的视频标准。本系统中采用其视频端口 0和视频端口 2,分别连接视频编码芯片和解码芯片,负责视频信号的采集和输出。通信控制模块包括两路标准RS232串口,其中一路连接系统控制面板,读取开关状态,控制面板指示灯,另一路连接火控计算机,接受火控计算机输出的火控系统参量信号, DSP控制其与原视频信号进行叠加复合,然后送监视器供 *** 作手观察。

2 系统软件设计

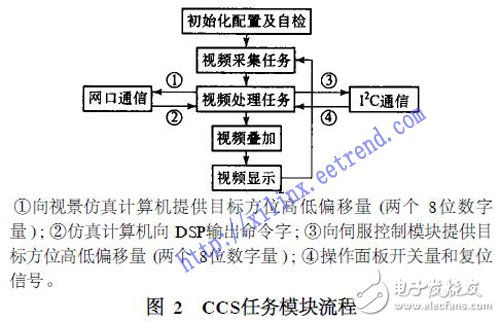

软件从功能上可分为图像采集、图像处理、识别跟踪、显示控制和主控等模块,主要完成视频采集、视频(帧信号)处理(预处理、二值化、目标识别、跟踪、预估) 、视频叠加、网口(视景仿真计算机)通信、IC通信(辅助控制板)和视频显示6个任务。

TI公司DSP开发环境为CCS,对应DM642的版本是2. 21, CCS中工作模式采用多线程处理方式,图2中各个功能块作为不同的任务分别创建、执行。

视频处理任务定时向辅助控制板报告其当前工作状态,如果处于锁定跟踪状态则送出目标偏移量,否则送出两个全零字节。然后,辅助控制板向DSP报告对 *** 作面板的监测结果。

为了防止多任务造成资源冲突,造成程序混乱,需要对它们执行的时序和调用关系进行控制。本系统采用了两种方法进行控制:

a) 使用SCOM (同步通信模块) 。SCOM的作用是在两个任务之间传递消息,对于两个有确定时序关系的模块,确保两者按照规定顺序执行,避免对共享区域形成读写冲突。

b) 使用临界段定义。对于时序关系不确定的两个任务,它们之间的共享数据定义为临界段代码,这使得其数据不能被一个以上的进程同时访问,并禁止其无关线程访问临界数据。否则,如果其他线程访问了其内部数据,可能使得整个程序处于异常状态,可能导致资源冲突、死机或者其他不良后果。本方法的缺点是临界数据不能过长,否则将使得程序执行缓慢。

电视监视器上需要显示的字符、波门信息供 *** 作者观察使用,其叠加任务由FPGA 实现。采用FPGA完成视频叠加任务的数字式电视跟踪系统的优点主要体现在以下两个方面:首先,系统中不可避免存在大量控制信号,需要进行较多的逻辑变化,为了避免分立器件带来的电路的繁琐,提高稳定性,可以充分利用FPGA空间,利用FPGA完成逻辑处理任务,从而不添加额外的逻辑控制电路。其次,在视频信号上叠加火控计算机送来的信号,包括目标高度量、距离量和速度量、跟踪波门、跟踪状态以及视场中心十字线。这些信息的叠加要求透明显示,能够实时刷新,而FPGA就能够达到上述要求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)