数据采集存储是信号处理过程的一个重要环节, 已经广泛应用于雷达、声纳、瞬态信号测试、无线探伤等领域。在不同的条件下采样速率和采样精度也有所不同, 系统的实现方法也各有差异。通常情况下, 如果采集速率较低, 采集和数据计算机读取可同时进行。但在高速采集或采集源移动的情况下, 如空中飞行体或水下运动体, 这时就需要系统有采集功能的同时应具有存储功能, 存储数据可事后读取, 黑匣子就属于这样的采集存储器。根据目前的发展趋势, 开发体积小、功耗低和存储容量大的系统越来越受到重视。根据实际情况, 我们研制开发了一种用蓄电池就可工作的、能在水下应用的、可回收的小体积低功耗的大容量存储器。

本文就介绍了一种基于FPGA 和FLASH 的多通道大容量的采集存储器的设计与实现方法。

1 系统背景及功能描述当船舶或潜艇在水中运动时, 要对其运动时的变化参数信号进行瞬态采集记录, 记录存储器要安装于运动的船体或艇体上的。要求采集存储时间不长, 但它必须要满足体积小、功耗低和可重复擦写功能。

此系统要求能对32 路模拟信号同时采集存储, 采样率是每路10KHZ, 总采样数率320K, 事后可对存储数据计算机读取分析。根据此种要求我们设计实现了多路采集存储器, 此种存储其使用FPGA 和FLASH 存储器。满足体积小, 功耗低的要求。用干电池供电就可工作。

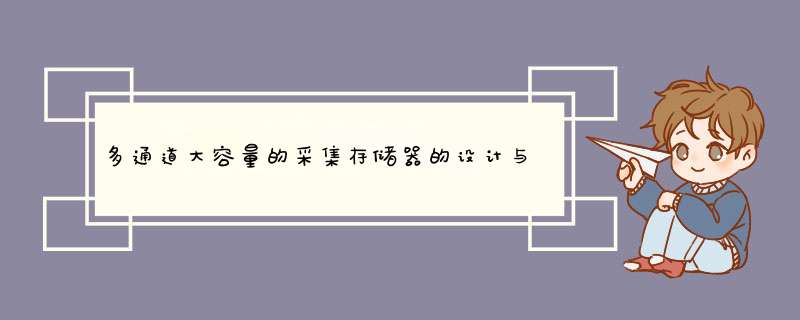

2 系统结构设计整个系统以FPGA 为核心控制器来组织工作, 它控制着整个系统的读、写、擦除等 *** 作。系统主要解决的问题是采集、存储和数据事后读取。

由于要同时对多路信号进行采集, 我们采取了FPGA 对模拟开关进行均等时间推进以实现通道的转换。当转换到某一通道时, FPGA 同时要启动A/D 进行模数转换。为了达到高精度采集的目的, 可采用12 位的AD 转换器。为了达到通道转换、启动A/D 和数据FIFO 存储的时序合理统一, 我们采用全体时钟, 实现过程如下图所示。

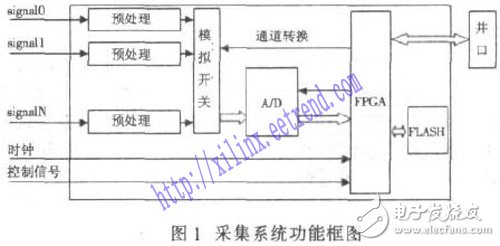

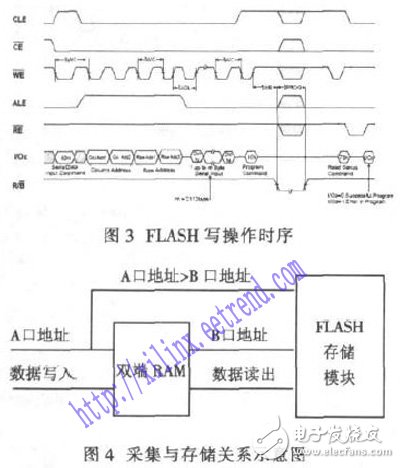

对数据的存储, 我们采用闪存(FLASH Memory)作为存储器, 它具有体积小、功耗低和数据不易丢失的特点。对FLASH的写 *** 作过程有其固定的 *** 作模式, 如图3 所示。由于FLASH是按页存储的, 当一页写完之后要进行下一页的控制字和地址的重新写入, 为了使采集回来的数据能及时准确的写入FLASH, 而不至于在页与页的交替时间内使数据丢失, 所以不可能将采集回的数据直接存入FLASH, 我们利用FPGA 内部提供的RAM来构成双端口RAM作为数据存储过程中的缓存, 采集回来的数据先写入双端口RAM, 然后再导入FLASH。过程是采回数据从A 口写入双端口RAM。双端口RAM中的数据从B口读出, 然后写入FLASH, 在 *** 作的过程中, 要保证双端口RAM的B 口地址推进要小于其A 口的地址推进。因为在采集过程中使用了12 的位的AD, 加之FLASH 存储器是8 位的存储器, 所以就使得每次采集的数据要分2 次存储, 我们采取的方式是高8 位存储一次, 低4 位加补标志码的存储一次。

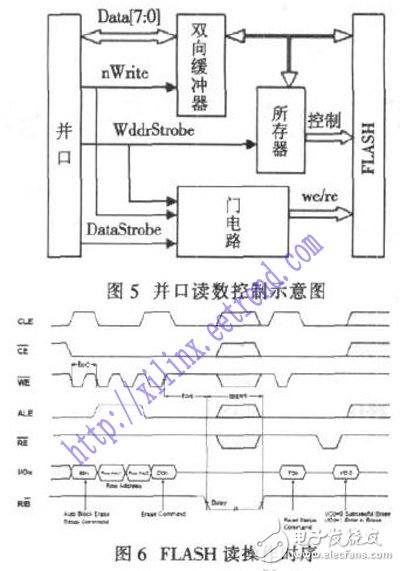

数据的读取有很多种方法, 目前有串口、并口、USB 口或PCI 总线方式读取。我们这里采用并口读取方式。因为数据存储量大, 我们采取了并口主动读取的方法, 消除了并口从动读取速度慢的问题, 采用EPP 模式, 读取数据速度能达到500K—2Mb/s 的数据量。FPGA 此时的工作是使读数和采集的控制线与数据线的隔离。

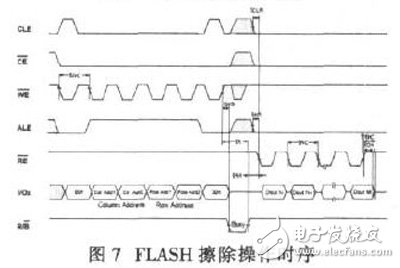

这时并口可直接对FLASH 的控制线和数据线进行 *** 作。对FLASH 的读数 *** 作也有其固定的 *** 作过程。FLASH 数据的擦除是按块擦除的, 所以它的特点是擦除速度快, 一般在几秒钟内就完成了。当一次采集存储完毕后, 数据就长久保持在FLASH 内, 不会丢失, 若要从新采集存储, 则必须要先进行FLASH 擦除。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)