最大的优点可能是当首个 SoC 芯片进入实验室时就可立即运行嵌入式软件。

作为基于 FPGA 原型方法的拥护者,有人可能会认为我们只片面地看到了这种方法的优点,而对其缺陷视而不见。但那绝非我们的本意。我们这本《基于 FPGA 的原型方法手册》旨在全面揭示基于 FPGA的原型的利弊,因为最终我们并不想看到有人本来可以使用其他方法更好地达到目的(比如说用基于System C的虚拟原型),却行进在这种方法的漫漫征途上。

让我们来更深入地研究一下基于FPGA原型方法的目的和局限性,以及其对于系统级验证和其他目的的适用性。把重点始终放在原型项目的目的上,让我们在平台、IP 使用、设计导出、调试及其他设计方面更容易地做出决策。这样,我们就能够通过分析世界上其他原型设计团队的案例,从他们的项目中汲取经验。

基于FPGA的原型可满足不同目的需求

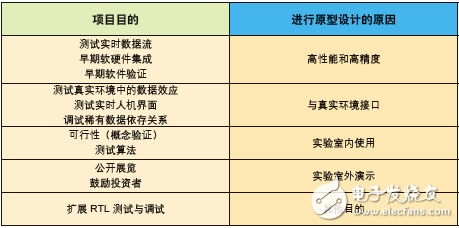

原型设计不是一个按几个按钮就能完成的过程,在它不同的阶段需要仔细的关注和思考。除说明这个过程需要完成的工作和涉及到的专业知识外,我们还应解释在 SoC 项目中该进行(或者不该进行)原型设计的原因。在与原型设计人员多年交谈中,我们最常问到的一个问题是“为什么您这么做?”。答案有多种多样,我们把它们总结成了表 1 中几条常见的理由。举例来说,“真实环境中的数据效应”,这可能指的是某个团队的工作是通过原型设计得到某个系统全速运行时的模型,并将其与其他系统或外设相连,目的可能是为了测试对某个新接口标准的合规情况。他们进行原型设计的大致理由是“与真实环境接口”,而且原型设计也确实在真正的芯片器件面世之前,提供了实现这个目的的最快、最准确的途径。

表 1 采用基于 FPGA 原型的常见目的与原因

系统了解这些项目的目的和我们进行原型设计的原因,将有助于我们判断基于 FPGA 的原型设计是否能为我们的下一个项目提供帮助。

因此,让我们探究一下表 1 所述的目的以及基于 FPGA 的原型方法如何能帮助实现这些目的。在许多情况下,我们还会给出真实环境中的一些实例,笔者藉此提前感谢那些奉献自己经验、指导他人走向成功的人士。

高性能与准确度

只有基于 FPGA 的原型才能提供正确测试设计各个方面所需的速度和准确度。我们把这个理由放在首位的原因是,虽然项目有许多需要实现的给定目的,但对需要进行原型设计的团队来说,这可能是所有理由中最根本的原因。举例来说,这个团队的目的可能是验证某些 SoC 的嵌入式软件,观察其在真实硬件上全速运行的情况,但使用原型的根本原因是为了确保高性能与准确度。我们在虚拟系统中可以在更高的性能水平下验证该软件,但我们无法达到使用真实的 RTL 所能实现的准确度。

实时数据流

难以验证 SoC 的原因之一是因为其状态取决于许多变量,包括其之前的状态、输入的次序以及更广泛的 SoC 输出系统效应(以及可能的反馈)。将 SoC 设计与系统的其他部分相连并以实时速度运行,可以让我们立即观察到实时条件、输入和系统反馈的变化带来的效应。

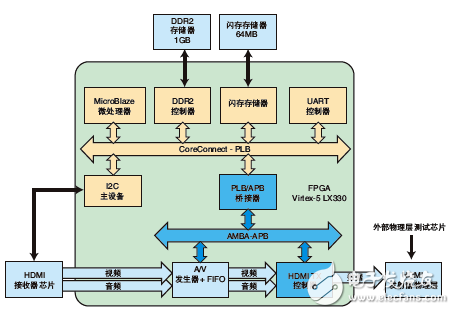

葡萄牙波尔图市 Synopsys 公司 IP 团队开发的 HDMI 原型中的实时数据流就是一个很好的例子。在本实例中,高清(HD)媒体数据流经处理内核的原型输出到高清显示器上,如图 1 的方框图所示。注意方框图底部显示的是实时音频和高清视频数据流,从接收器(从外部源)接收,流经原型,输出到与外部监控器相连的实时HDMI PHY 的整个流程。

通过使用投片前的原型,我们可以立即看到和听到不同的高清数据在我们的设计上的效果,反之亦然。只有采用基于 FPGA 的原型方法才支持这种实时数据流,不仅给此类多媒体应用带来极大好处,也能给许多其他要求对输入数据流做出实时响应的应用带来诸多裨益。

图 1 HDMI 原型方框图

软硬件集成

在上述实例中,读者可能已经注意到原型使用了一块小型 MicroBlazeTM CPU,并备有外设和存储器,从而体现了一个 SoC 的所有常见模块。在这个设计中,运行在 CPU 上的软件主要用于加载和控制 A/V 处理。然而,在许多SoC 设计中,软件最耗精力。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)