2012年度国际电子元件大会(IEDM)于美国时间12月10日在旧金山登场,与会专家表示,半导体制程迈向 14奈米节点时,可能无法达到通常每跨一个世代、晶片性能可提升30%的水准,甚至只有一半;但仍会增加大量成本,主要是因为新制程节点缺乏所需的有效微影技术。

欧洲研究机构 IMEC 执行长Luc van den Hove在IEDM发表专题演说后对EETImes美国版编辑表示,晶片制造商目前已经进入28奈米制程节点,距离14奈米节点虽还有两个世代,但现在必须决定微影技术选项;不过具潜力的超紫外光(EUV)微影工具,可能要到2014年才能做有限度的商业用途。

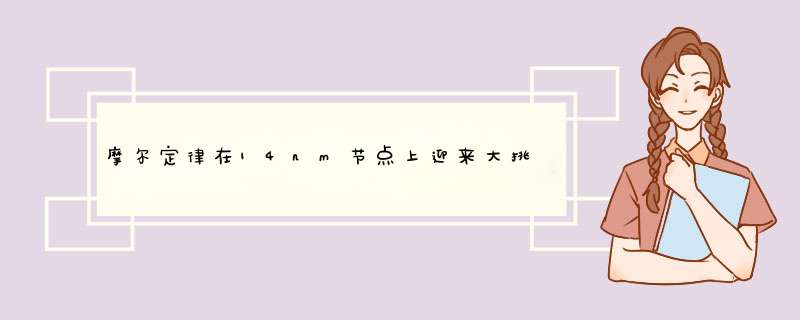

van den Hove在专题演说中指出,14奈米制程若采用现有的193奈米浸润式微影设备,所需成本将比28奈米制程多90%以上;EUV技术则能将成本增加幅度减至60%左右。成本增加主要是因为若在14奈米节点采用现有微影系统,最多得要三次曝光;但采用EUV技术,只需要一次曝光。

14奈米制程与28奈米、20奈米的成本比较

IMEC 微影技术专家Kurt Ronse表示:「三重图形(patterning)实在是太复杂,因此得放宽设计规则,但如此一来晶片就达不到良率。」因此他指出,14奈米晶片的性能可能只会比上一世代提升15~20%,而不是传统每跨一个世代提高30%的水准。

「看来在14奈米制程节点,有部分设计规则必须做某种程度的放宽;」van den Hove在专题演说中表示:「我认为此时此刻得决定14奈米节点微影技术选择是最基本的,但EUV显然还无法因应该制程节点挑战。」

「要解决(EUV)问题还得花费很大工夫;」van den Hove补充指出:「不过我们相信问题并不在于其理论基础,而是需要时间来处理的工程性问题。」

今年稍早,一位英特尔(Intel)高层表示,该公司认为能以经济的方法运用四重图形(quad patterning),在不需EUV技术的情况下前进至10奈米制程节点。而英特尔的晶片制造成本向来被认为比其他厂商来得高,不过该公司的处理器晶片售价也相对较高。

包括英特尔、三星(Samsung)与台积电(TSMC)在今年分别对半导体设备业者ASML注资数十亿美元,因为ASML是最有力的EUV系统供应商;ASML在今年还收购了一家微影设备光源供应商Cymer,后者可提供EUV所需的更有效光源。

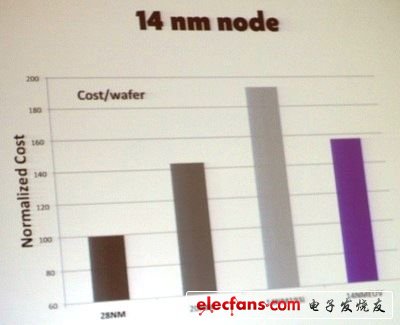

Ronse指出,使用目前的光源设备,EUV系统的制图速度一小时不到20片晶圆;而晶片供应商需要的微影系统,是能达到每小时100片以上晶圆的制图速度。IMEC到目前为止已经协助半导体业者进行过数千片的EUV晶圆测试。

IMEC的EUV系统产出量测试结果

而IMEC的研究人员也表示,晶片制造商若要延续摩尔定律(Moore‘s Law)的生命,可能得采用新的材料或是元件型态。

新材料是延续摩尔定律的关键

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)