赛灵思的7系列FPGA和Zynq器件创造性地在片上集成了模数转换器和相关的片上传感器(内置温度传感器和功耗传感器),这是相比赛灵思前一代产品来新增加的特性,可在系统设计中免去外置的ADC器件,有力地提高了系统的集成度。本文就这一新模块的使用进行简单介绍,希望对大家有所帮助,当然如有不当之处还请高手指正,以免误导大家,欢迎大家补充。

2.XADC模块介绍

2.1 XADC模块概述

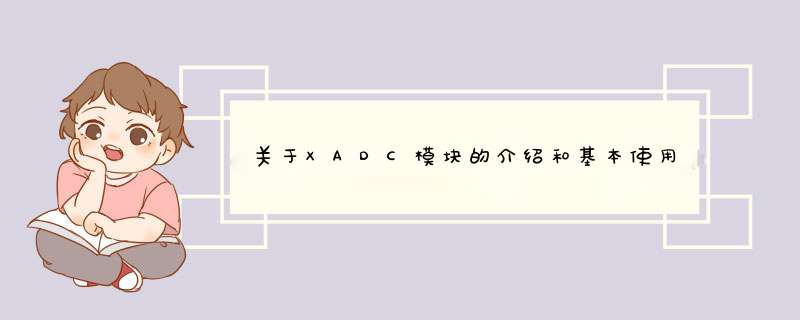

Zynq器件XADC模块包括2个12比特1 MIPS的模数转换器和相关的片上传感器,模数转换器能为系统应用提供通用目的的高精度的模拟接口,下图是XADC模块的框图:

XADC模块支持不同的 *** 作模式,如外步触发同步采样模式;可接受不同类型的模拟输入信号,如单端或差分信号;最多能接受17路外部的模拟输入信号。XADC模块也包括一定数量的片上传感器用来测量片上的供电电压和芯片温度,这些测量转换数据存储在一个叫状态寄存器(status registers)的专用寄存器内,可由FPGA内部叫动态配置端口(Dynamic

ReconfiguraTIon Port (DRP))的16位的同步读写端口访问。ADC转换数据也可以由JTAG TAP访问,这种情况下并不需要去直接例化XADC模块,因为这是一个已经存在于FPGA JTAG结构的专用接口,此时因为没有在设计中直接例化XADC模块,XADC模块就工作在一种预先定义好的模式叫缺省模式,缺省模式下XADC模块专用于监视芯片上的供电电压和芯片温度。XADC模块的 *** 作模式是由用户通过DRP或JTAG接口写控制寄存器来选择的,控制寄存器的初始值有可能在设计中例化XADC模块时的块属性(block attributes)指定。

2.2 XADC模块管脚需求

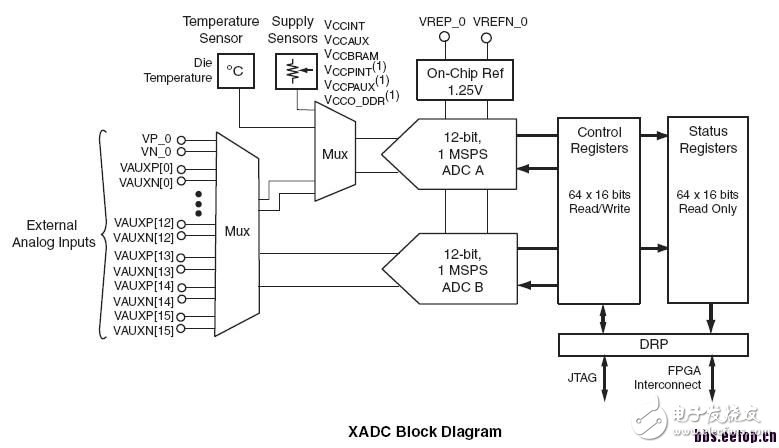

所有的XADC模块专用管脚都位于bank0, 所以都加有_0的后缀。下图表示了XADC的基本输入输出需求:

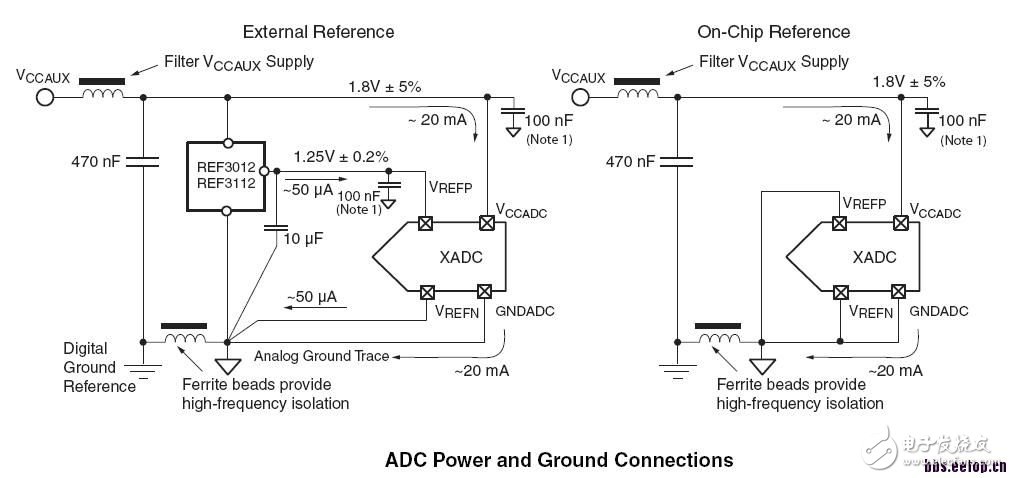

这有两种推荐配置:图中左边XADC由Vccaux(1.8V)供电,并且用一个外部的1.25V参考源。用外部参考源在精度和热飘移方面可以获得更好的性能,一个磁珠用隔离模拟地和数字地,这可避免较常用的模拟和数字电路共地而把噪声带入模拟电路的缺点;图中右边XADC是用片内的参考源,这时VREFP脚必须按图中所示连接到地。

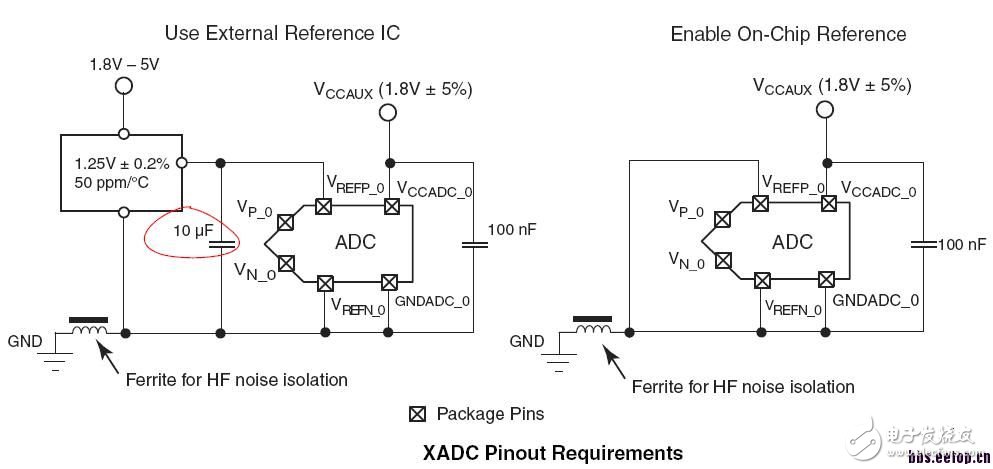

下表列出了XADC相关的引脚和连接:

注:XADC模块有一专用的支持差分输入的模拟通道输入引脚(VP/VN),另外还最多有16个辅助的模拟通道输入引脚(ADxP or ADxN,x为0到15),Kintex-7不支持辅助通道6,7,13,14,15。Zynq-7000 AP SoC器件由于封装不通可能不会支持所有的辅助通道,具体要查询封装文件。

3.基本使用方法

3.1 XADC模块的 *** 作模式

最基本的 *** 作模式叫缺省模式,缺省模式下XADC模块专用于监视芯片上的供电电压和芯片温度,这时XADC模块并不需要用户对其进行配置。

另外一个为同步采样模式,按预定的步骤顺序采样两个外部的模拟输入信号,并把采样结果存储在状态寄存器内。

单通道模式,在这种模式下,用户必须通过写控制寄存器40H的CH4到CH0比特来选择一个要采样的通道。另外控制寄存器40H的BU(analog input mode)和ACQ(settling TIme)两个参数也必须设置。

独立ADC模式,在这种模式下,ADC A是固定用来实现一个类似于缺省模式的“监控模式”,报警输出功能是有效的,用户必须设置正确的报警门限;ADC B只能用来测量外部的模拟输入。

Single Pass模式,在这种模式下,按用户选择的采样顺序序列顺序采样一遍后停止ADC。

采样顺序序列是由用户写序列通道选择寄存器48H和49H来设定的。

ConTInuous Sequence连续序列模式,这种模式和Single Pass模式很相似,区别是采样完一遍后系统自动重新开始序列采样,故为连续采样。

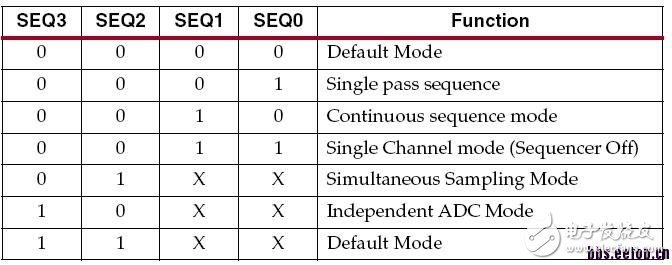

模式选择是由控制寄存器41H的SEQ3到SEQ0比特决定,具体如下图示:

3.2 XADC primiTIve

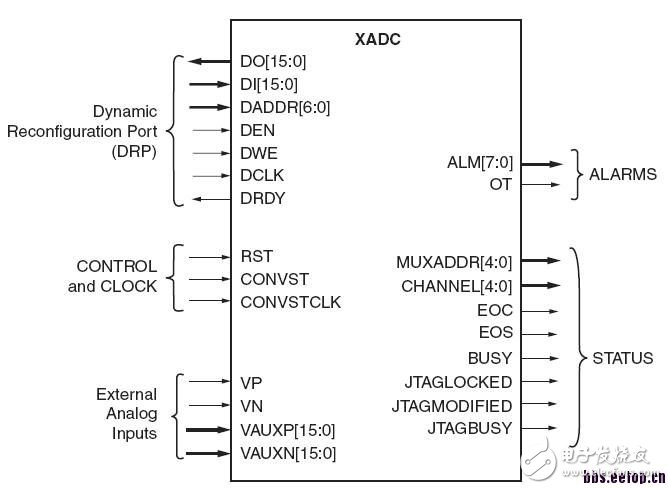

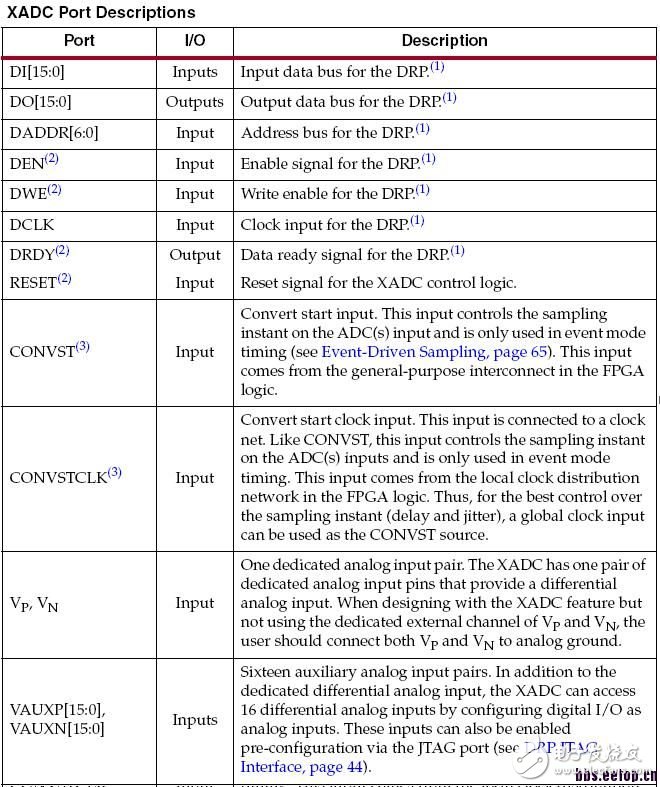

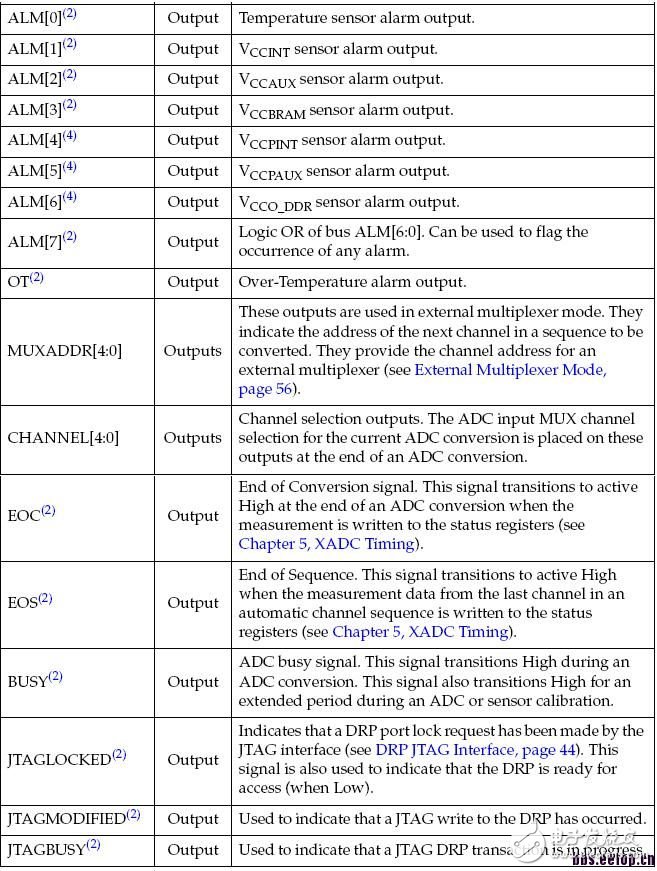

XADC模块的使用方法,一是直接用FPGA JTAG专用接口访问,这时XADC模块工作在缺省模式;二是在设计中例化XADC模块,这是可以通过FPGA逻辑或ZYNQ器件的PS到ADC模块的专用接口访问。例化XADC模块有两种基本形式:一是ISE和PlanAhead环境下LogiCOREIP核的形式调用,二是EDK环境下对LogiCOREIP核的调用。这两种调用方法相信对使用过XILINX产品的朋友来说 *** 作界面与步骤都很熟悉,这里就不赘述了,主要是想说明下XADC模块原语,以期对这模块有个基本的了解。下图是XADC模块的输入与输出端口的示意图:

各引脚功能描述如下:

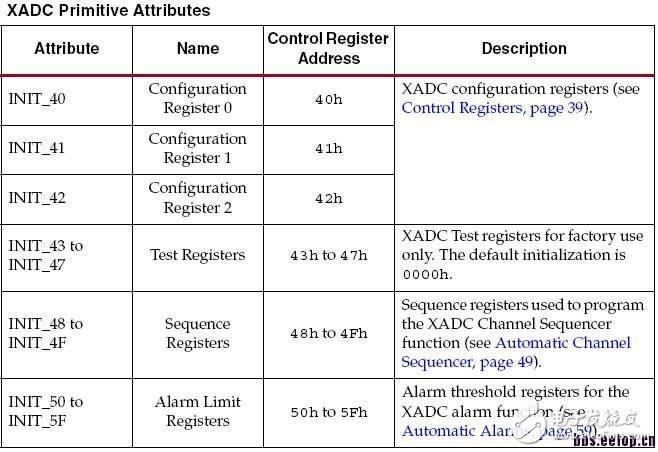

XADC可配置的属性如下图示(等效于配置相应的寄存器):

4.PCB要点

模数转换器所能获得的精度和PCB设计关系很大,因为模数转换器是敏感的部件,它的模拟接口容易受到噪声的影响,下面就PCB设计时要注意的地方做一简单介绍。

1). 典型应用中VREFP 和 VREFN外接1.25V参考电压,电压精度为± 0.2%,并且在PCB上要尽可能的靠近VREFP 和 VREFN引脚,并且按电源IC要求使用合适的去耦电容。

2). 如果使用片内的参考电压,VREFP 和 VREFN引脚要通过一磁珠连到模拟地,以去除高频干扰。

上面两种情况的电源连接情况如下图示:

注意隔离数字电源和模拟电源的磁珠应使噪声对模拟电源供应的波动小于1 LSB (250 uV),这在用12比特测量时可以最小化噪声对精度的影响。作为一个通用原则,模拟地和数字地要分开,以减少噪声从地平面耦合过来的影响。

3). 尽量在每个引脚放一个100nF的去耦电容,PCB上尽量靠近引脚。

4). 外接1.25V参考电压接VREFP 和 VREFN引脚时,PCB上应该用紧密耦合的差分对形式布线,它们应该走线在同一层,使用最小间隔,可以用模拟电源和模拟地来隔离保护它。

5). 外部模拟输入引脚采用差分输入形式可以有效地去除共模噪声,两个差分输入应该按紧密耦合的差分对形式布线,使用最小间隔,推荐在输入端应该放置抗混叠滤波器,这个抗混叠滤波器应该尽可能地靠近FPGA。

5.参考文献:

以上介绍抛砖引玉挂一漏万地,详细的说明还需要大家认真阅读XILINX官方出的原始文档,下面列出这些主要的参考文献供大家进一步学习研究:

[1].Xilinx UG480: 7 Series FPGAs and Zynq-7000 AllProgrammable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User Guide

[2].Xilinx UG772: LogiCORE IP XADC Wizard User Guide

[3].Xilinx PG019: LogiCORE IP AXI XADC (v1.00.a) Product Guide

[4]. Xilinx UG585:Zynq-7000 All ProgrammableSoC Technical Reference Manual

[5].Xilinx XAPP554: XADC Layout Guidelines

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)