实时视频图像处理技术的应用十分广泛,在民用领域有机器人视觉、资源探测和医学图像分析等;在军用领域有导d精确制导、敌方目标侦察与跟踪等。

本设计中采用了DSP+FPGA的硬件结构,DSP采用ADI公司的高性能双核DSP-BF561作为主处理器,负责整个算法的调度和数据流的控制,完成图像数据的采集与显示及核心算法的实现;而FPGA作为DSP的协处理器,依托其高度的并行处理能力,完成图像预处理中大量的累乘加运算。DSP的2个内核与FPGA通过中断进行通信响应,使系统的各处理器并行工作,提高了DSP内核及FPGA的利用效率,保证了系统采集与显示的实时性。

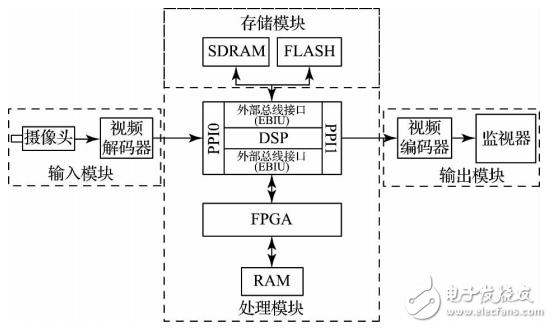

2、系统原理与结构图像采集与处理系统主要包括4大模块:图像采集模块、存储模块、处理模块和显示模块。图1所示为DSP+FPGA的图像采集与处理系统硬件结构框图。

图1 图像采集与处理系统硬件结构

系统的前端输入模块由CCD摄像头及视频解码器7181B实现,视频解码器将CCD接收到的模拟视频信号转换为标准的YUV4∶2∶2数字视频格式,图像大小为720×576。转换后的图像数据通过ADSP-BF561的专用视频接口PPI0先存储到RAM中,当采集完一帧图像数据时DSP的DMA产生中断,此时FPGA首先对采集来的图像数据完成图像的预处理,然后DSP再将预处理的数据取回完成相应图像处理算法,最后通过PPI1接口由DMA控制器将处理完的视频数据送到视频编码器7171,转换成标准的模拟PAL视频信号到监视器上进行显示。FLASH的作用是存储系统运行的程序,引导系统的启动。

针对系统要求,DSP选用AnalogDevices公司的ADSP-BF561处理器,该DSP是专门针对多媒体和通信应用方面的一款16位定点DSP,它集成了2个Blackfin处理器内核,每个内核可实现600MHz持续工作。

FPGA选用Altera公司的EP2C5,它拥有4608个逻辑单元,13个18×18硬件乘法器,多达142个用户自定义IO口。

2.1、采集模块设计CCD摄像头采集来标准的PAL制式模拟视频,设计选用ADI的ADV7181B视频解码芯片对模拟信号进行A/D转换。ADV7181B是Analog公司的一款应用广泛的视频解码芯片。该芯片可以自动检测输入的复合视频信号,通过I2C总线配置接口,可选择图像输出格式。由于黑白图像已能够满足系统的检测需要,因此把模拟信号以ITU-R-656格式YUV(4∶2∶2)输出。Y信号是亮度信号,U、V信号是色度信号。这样就可以直接提取该格式的亮度信号, *** 作比转换为传统的RGB格式要简单得多。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)