选择WSN的晶格拓扑结构是因为它通常被用于WSN的测量应用中,也允许:1)试验可重复;2)从不同的节点同步传输数据;3)可选择路径以防节点失败。

10×10节点的晶格拓扑结构被用来做这次的测试,所有节点和节点100的延迟假定在考虑中。值得注意的是,选择一个不同的参考节点只会在节点之间的延迟的趋势增加一个偏移量,但不会改变延迟的统计特性。这就保证了我们发现的性能和特征在广泛意义上是普遍适用的,不会因为个体差异有特别大的变化。

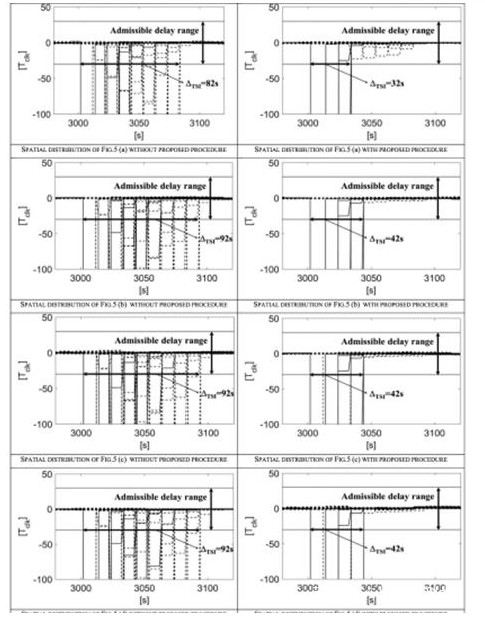

在ASN同步之后3000s实现了NSN的插入。可以认为如果任何一对节点之间的延迟在等同于3σs时相应的30Tclk条件下在容错范围内变化,那么同步是可以实现的。容错范围是根据在一些控制应用中的σs选择的。考虑到NSN拓扑结构的空间分布,进行了4次实验,如上面的图所示,由黑色的节点标明。选择这种NSN的空间分布是因为他们是基本的分布,更复杂的情况可以通过结合和改变它们来获得。

下面的表展示了每个实验的数据:采用或不采用所提出的程序来过滤来自NSN的信息时,所有节点和节点100之间的时间延迟的趋势。NSN的延迟的趋势用黑色粗体线条描绘。这种情况下提出的程序是不能用的,ASN之间的同步精确度并不会被保存:ASN之间的时间延迟已经超过了容错范围,不被我们所允许考虑。在这种情况下,提出的程序是可以用的:ASN之间的同步精确度可以保存并且NSN会向基于ASN的时钟时间值的参考时间收敛。

在试验1和试验2中,ASN几乎都和3个NSN、5个ASN连接。在两次实验中,ASN之间的同步精确度只有在使用所提出的过滤程序时才被保存。在试验3中,节点65仅与NSN连接。采用所提出的程序,只有节点65的同步精确度降低了,其他的ASN保持不变。不适用所提出的程序的话,所有的ASN同步精确度都会降低。

在测试4中,节点65和7个NSN、1个ASN连接,节点55和4个NSN、4个ASN连接。使用所提出的程序,只有节点65降低了同步精确度,其他ASN保持不变。不适用所提出的程序,所有ASN的同步精确度都降低了。

在所有的测试中,采用所提出的程序同步WSN的时间间隔对于不采用时的情况减少了超过50%。每个NSN执行相同的ASN同步程序的事实证明以上观点,因此每个NSN从I(tk)执行它自己的值,而且只基于ASN计算α^j(tk)和o^j(tk)。最终的效果是:1)NSN不会影响ASN,因为它的信息被忽略了;2)ASN在NSN加速向参考时间收敛时有强烈影响。

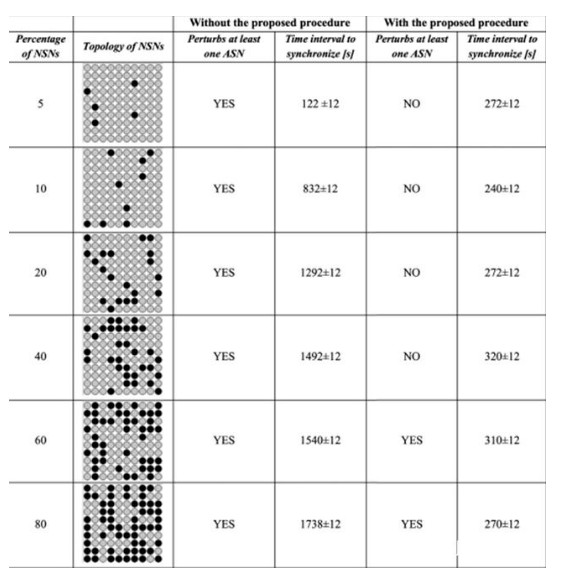

进一步的测试通过考虑全连接拓扑结构和插入不同比例的NSN来执行。由于NSN的全连接,节点的分布对同步精确度没有影响。因此,这些测试提供指示,得知关于ASN所选择的NSN的空间分布是否会扰动ASN的同步精确度。

NSN的空间分布是随机选取的。采用所提出的程序,ASN的同步精确度不会受到扰动,直至60%的NSN节点被插入。不采用所提出的程序,5%的NSN节点被插入时就会降低ASN的同步精确度。此外,还可以指出的是,在不采用所提出的程序的示例中,在NSN插入后WSN同步所需的时间间隔是由NSN的数量决定的,而在采用所提出的程序时是独立的。当解决方案是TO=2 s时估测出ΔTIS。ΔTIS的改变取决于同步周期TP=10 s。事实上,在案例中有些NSN是在 tk前添加进来的,它们在 tk时开始同步,其他的在tk+1=tk+Tp。因此,ΔTIS最大的变化是12s.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)