确保多重FPGA电轨依正确顺序关闭,跟确保开机程序是否正确一样重要,可避免装置因电压状态无法判断而提早故障。

电源定序避免损坏

在启动目前的大型系统单晶片FPGA的多重电轨时,有许多技巧可用来控制其启动顺序和时序。遵照装置制造商所指定的正确顺序甚为重要,如此可避免装置抽取过多电流而导致损坏。

有些方法是透过 *** 纵各转换器的电源良好输出,来控制顺序中下一个供应的Enable脚位。如需要继电器,可插入电容器。另一种类似的方式则是使用重置IC,在前一个供电达到所要的电压后启动下一个转换器。每种方法都有一些缺点,且这些方法都无法控制电源关闭的顺序。依正确的相反顺序关闭电轨,跟开启电源顺序是否正确一样重要,都是为了确保装置能安全运作。

图1 透过定序IC管理FPGA电轨。

定序器维持电源关闭控制

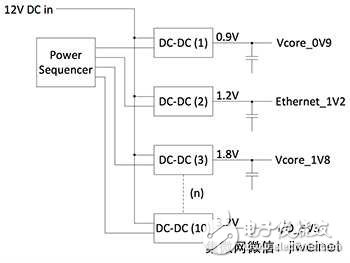

使用具有已知时间常数的电路,主动将去耦合电容器放电,定序器便能维持正确的电源关闭顺序,其做法是在串联的电容器中暂时插入放电电阻器。图2显示如何在加入最少必要元件下,使用一对细心挑选的MOSFET将电阻器插入电路中。

图2 控制电源定序的主动放电电路。

电源定序器的EN输出连接到DC-DC稳压器的Enable脚位,也连接到P通道MOSFET(Q1)的闸极。定序器输出降低停用DC-DC稳压器时,Q1便会反转讯号,开启N通道MOSFET Q2。开启时,Q2会透过R2电阻使15mF去耦合电容器放电到接地。

图中的电路假设DC-DC稳压器在提供关机讯号后无法持续产生输出。假如DC-DC稳压器的输出能在收到关机指令后持续供应电源,则需要额外的继电器才能启动放电电路。

选择的R2值必须能确保适当的放电时间,让定序器能在可接受的时间间隔内完成关机。另外还要注意的是,电阻必须够大,才能避免电流尖峰值上升率过快,避免引发EMI问题,以及对Q2和去耦合电容器组造成瞬态热应力。实务上,选择R2值时需考虑一些额外的重要参数,像是Q2的导通电阻(RDS(ON))和电容器组的等效串联电阻(ESR)。

选择MOSFET Q1时应参考电源定序器的输出电压阈值。所选的装置应有够高的闸极阈值电压(VGS(th)),确保定序器输出为高电位时能保持关闭,但要注意的是,VGS(th)会随接面温度上升而下降。本范例中选择的定序器 *** 作供应电压为5V,最小指定高电位输出电压为4.19V。Q1的VGS(th)在60℃环境 *** 作温度下必须大于0.9V,以确保运作正常。此外,闸极应使用100kΩ电阻下拉至源极电位,以避免误开。查看MOSFET资料表中VGS(th)与温度的标准化曲线,显示Diodes公司的ZXMP6A13F符合要求:保证最小VGS(th)在室温下为1V,到60℃则下降至0.9V左右。

在此范例中,我们假设定序器必须在100ms内关闭总共10V的电轨。因此,每个电轨的去耦合电容器组必须在10ms内完成放电。目标是达成RC时间常数8ms的3倍,确保电容器在要求时间内放电到全电压的5%以下。计算RC常数时,电容器组的MOSFET RDS(ON)、寄生线路电阻和ESR都必须与电阻器R2一同纳入考量。

假设电容器ESR和线路电阻加起来不超过10mΩ,去耦合电容器组的总电容值为15mF,则RDS(ON)和R2的适当值可用下列运算式求得:

3x(10mΩ+R2+(1.5×RDS(ON)))×15mF=8ms

假设R2=50mΩ,功率MOSFET Q2的RDS(ON)在VGS=4.5V且环境温度为25℃下必须小于80mΩ。

选择MOSFET时,温度相关变动的效应和RDS(ON)的批量变异也应考量在内。RDS(ON)在4.5V闸极驱动下、超出预期作业温度范围时的变异可能高达15mΩ。因此最好的做法是,确定R2为所选MOSFET之制造商指定最大RDS(ON)的两倍左右。如果R2为50mΩ,则可选用Diodes公司的DMN3027LFG N通道MOSFET。此装置在VGS=4.5V、室温下的RDS(ON)典型值和最大值分别为22mΩ和26.5mΩ。因此,RDS(ON)变化可从15mΩ到40mΩ,放电时间从95%(3倍RC)的3.9ms起跳,使用最差20mF大小的电容器组时放电时间则可能拉长到5.4ms。

评估最大单一脉冲保护MOSFET安全

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)