航空电子是指飞机上所有电子系统的总和。一个最基本的航空电子系统由通信、导航和显示管理等多个系统构成。航空电子设备种类众多,针对不同用途,这些设备从最简单的警用直升机上的探照灯到复杂如空中预警平台无所不包。而航空电子系统也有着只属于自己的特点,这些特点更是随着航空电子的发展而不断变化。

MIL-STD-1553简介请看一下数据传输路径,即图1中的MIL-STD-1553总线结构。MIL-STD-1553是一种定义数据总线的电子和协议特点的军用标准。作为一种在军用和商用领域广泛应用超过25年之久的总线,并且符合MIL-STD-1553标准,它能以1Mbit/s的速率高度精确、极为可靠地传输数据。

根据MIL-STD-1553标准的规定,总线结构由三个不同的硬件组成:

●总线控制器——总线控制器是总线上唯一允许在数据总线上发出命令,并负责引导数据总线中数据流的硬件设备。如果同时有几个终端可以实现总线控制器的功能,同一时间内只能有一个处于活动状态。

●总线监视器——总线监视器是一个可以监控总线上信息交换的终端。它可以用于飞行测试记录、飞行故障诊断、维护记录与任务分析,同时还可作为一个备用总线控制器,它有足够的信息可以接替总线控制器。然而,总线监视器是一个被动的设备,它不能报告所传输信息的状态。

●远程终端——每个远程终端都包括在数据总线和子系统间传输数据所必须的电子器件和支持性中间件。对于MIL-STD-1553,子系统就是所传输数据的发送者和接收者。这些终端不能作为总线控制器或总线监视器使用。

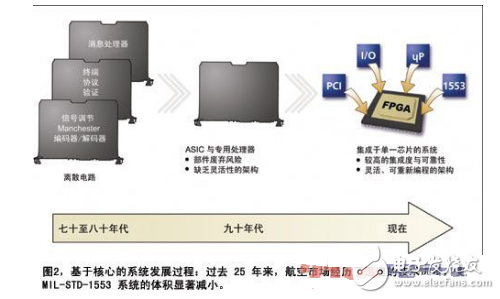

MIL-STD-1553系统实施像其它军用网络技术一样,航空电子市场中的MIL-STD-1553测试和仿真实施也经历了从庞大的DECUnibus卡到19英寸的通过机架安装的组件,又发展到用于VME和PCI系统上的较小、较为集成的多通道背板,现在又出现了更小、集成度更高的PCMCIA接口。图2描述了专用的MIL-STD-1553ASIC芯片制造商的实施从离散的协议和收发器芯片组精简到单一的体积小、功耗低的ASIC的发展过程。

FPGA有多种密度,通常以逻辑单元或门来度量。它们有多种形式架构,提供了丰富的I/O引脚可供使用。FPGA还可提供内部存贮器。例如,当前由Xilinx推出的一流的FPGA存贮容量比三年前约增加了10倍。而且还提高了内部速度,降低了成本。

现代FPGA海量的存贮和功能使其成为MIL-STD-1553设计最理想的选择。其核心为预先定义的、且经过测试的功能,这些功能可以应用到FPGA设计中。促使工程师们为MIL-STD-1553实施选择IP设计的原因有很多,其中包括:

废弃部件管理——利用IP核心可以显著地降低废弃的风险。设计师不会束缚于某一个特定的部件、甚至是FPGA制造商。这与随时可能会被放弃的单一来源的专用MIL-STD-1553协议ASIC和处理器(及其制造方法)形成了鲜明的对比。对电路实施FPGA后,设计可移植到最新的FPGA中,一般都无须改变其功能,减少了对软件的修改(通常是项目中成本最大的部分)。

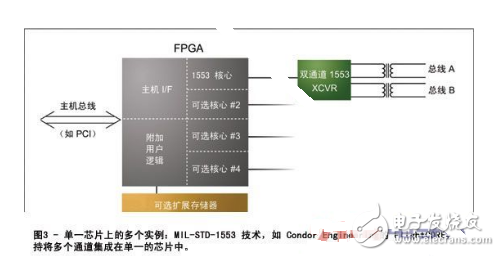

减小体积、提高可靠性、降低功耗和重量——将多种功能,包括处理器、I/O、MIL-STD-1553和背板电路综合到单一的IC中,可显著地减少部件数量、板卡空间和热负荷。这样就增加了可靠性,进而提高了MTBF。减少部件数量可以降低飞行设备系统对重量、空间及功耗的需求。如图3所示,设计人员可以将多种功能综合到单一的逻辑设备中,减少了部件的数量和体积。

降低成本——由于实施了FPGA核心,生产和生命周期的成本会随着时间而下降。FPGA价格历来是随着项目的进行而显著地下滑,而ASIC在长期的生产过程中价格却会上涨。很多航空电子系统已经在其设计中采用了FPGA,一个MIL-STD-1553核心实例可以轻松地融入现有的芯片或同系列的其他更密集的芯片中。单一FPGA中集中了多通道实例可进一步节省成本,只因为单一FPGA内可以容纳多个通道接口。

便于重新编程——由于支持对现场硬件的重新编程,核心的实施显著降低了设计风险。如果系统需求发生变化,或者要修复一个错误时,基于FPGA的设计可以在软件的控制下进行升级。这种灵活性还可以在硬件构造完成后,在硬件和软件间重新区分功能。例如,如果在集成阶段发现软件不能有效地响应一个实时事件,可以将该功能下移到FPGA级别,这样就将原由软件实现的功能转化为硬件功能。

适应多种机体——灵活、可重新编程的解决方案适于为多种机体构架或针对多用途基础设计的飞航测试线上可更换件(LRU)。由于USAF和NATO的多种机体采用从MIL-STD-1553B标准分离出来的协议,所以多种机体的LRU需要灵活、可编程的设计。某些设计实施了通过特殊的子地址或模式代码协议进行寻址扩展的数据集。很多固定翼和可旋转翼飞机同时采用了较老的MIL-STD-1553A和MIL-STD-1553BLRU,这就要求总线控制器和总线监视器能够处理不同的协议。

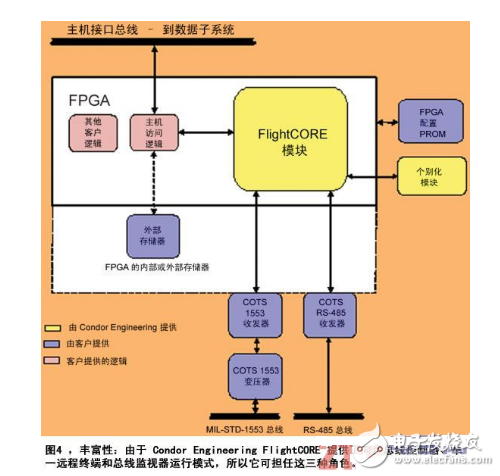

对MIL-STD-1553系统设计采用基于核心的实施现代FPGA的强大功能使其成为MIL-STD-1553设计的理想选择,这就是CondorEngineering推出FlightCORE的原因。FlightCORE是一种允许设计人员在各种Altera和Xilinx的FPGA中轻松实现无版权的实例化设计的MIL-STD-1553IP。多数情况下,利用Xilinx综合技术(XST)或AlteraQuartusII集成综合技术(QIS),FlightCORE1553可以在两天内成功地集成。如图4所示,用户只须将CondorEngineering的IP核心与其自身逻辑和CondorEngineering的个别化模块(3mmx3mm)集成,即可实现高性能的MIL-STD-1553设计。FlightCORE还允许开发人员选择存储器的大小以恰好地与其系统需求相匹配。图4还显示了可以实施内部存贮和/或外部双端口随机存贮器。该产品还提供了ManchesterII编码与解码、信息协议验证与合法化及为接口控制和编程实施简单的共享存贮架构等所有的必要组件。只需增加外部收发器即可,如标准的COTSMIL-STD-1553或RS-485收发器。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)