嵌入式FPGA(eFPGA)是指将一个或多个FPGA以IP的形式嵌入ASIC,ASSP或SoC等芯片中。

换句话说,eFPGA是一种数字可重构结构,由可编程互连中的可编程逻辑组成,通常表现为矩形阵列,数据输入和输出位于边缘周围。 eFPGA通常具有数百或数千个输入和输出,可连接到总线、数据路径、控制路径、GPIO、PHY或任何需要的器件。

所有eFPGA都将查找表(LUT)作为基本构建模块。 LUT有N个输入选择一个小表,其输出表示N个输入的任何需要的布尔函数。 有些eFPGA LUT有四个输入,有的有六个。有些LUT有两个输出。 LUT通常在输出端具有触发器; 这些可以用来存储结果。这些LUT寄存器组合通常以四进制形式出现,还有进位算术和移位器,以便有效地实现加法器。

LUT接收来自可编程互联网络的所有输入,并将其所有输出反馈到可编程互连网络。

除了LUT之外,eFPGA还可能包含MAC(乘法器/累加器模块)。 它们也连接到可编程互连网络,用于提供更高效的数字信号处理(DSP)和人工智能(AI)功能。 对于内存来说,有大量的RAM,通常是双端口的封装。至于LUT和MAC,通过RAM连接到可编程互连网络。

eFPGA具有输入和输出引脚的外环,将eFPGA连接到SoC的其它部分,这些引脚也连接到可编程的互连网络。

软件工具用于合成Verilog或VHDL代码,以编程eFPGA逻辑和互连来实现任何所需的功能。

eFPGA是方便的新逻辑块,可在许多方面提高SoC的价值,其中包括:

使用数百个LUT的广泛,快速的控制逻辑;

可重新配置的网络协议;

用于视觉或人工智能的可重构算法;

用于航空航天应用的可重配置DSP;

用于MCU和SoC的可重配置加速。

除了以上这些,还有更多,这里就不一一介绍了。

当今,已经有了一些eFPGA供应商,主要包括Achronix,Flex Logix,Menta和QuickLogic,此外,还有一些较小的供应商。有了这些选择,客户需要决定哪一个最能满足他们的需求。那么,要如何选择呢? 虽然需要考虑商业因素,但本文重点讨论技术因素。

第1步:制程的兼容性

通常情况下,即使在IP评估的早期阶段,公司也会选择foundry厂和工艺节点。而台积电、GlobalFoundries和SMIC现在或正在开发针对包括65nm,40nm,28nm,22nm,16nm,14nm和7nm工艺节点的eFPGA。

但是,并非所有供应商对所有代工厂/工艺节点都有eFPGA,至少目前还没有。 通过他们的网站检查哪些与您的制程兼容非常重要。 您还应该看看所讨论的eFPGA是否已经在芯片中进行了验证,并在NDA下提供了报告。

不要忘记检查金属堆栈的兼容性。您选择的关键IP,如SerDes或您的应用可能需要您使用特定的金属堆栈,但并非所有eFPGA IP都与所有金属堆栈兼容。

第2步:阵列大小和功能

并非所有的eFPGA供应商都可以做非常小规模的eFPGA,同时,并不是所有厂商都可以做出规模非常大的eFPGA。另外,它们支持的MAC和RAM的性质可能会有所不同。

对于您是否需要数百个LUT或数十万个LUT,以及您对MAC和RAM的需求,这可能会筛选出一些供应商。

步骤3:使用RTL进行基准测试

eFPGA供应商会为您提供用于评估的软件,以便您可以确定(RTL)每个eFPGA可以实现的硅面积和性能。您需要eFPGA能够在与SoC其余部分相同的温度和电压范围内运行,因此请确保您需要的是支持的。

在进行基准测试时,将苹果与苹果进行比较(compare apples to apples)非常重要。例如,您应该在相同的工艺(slow/slow or typ/typ or fast/fast)以及相同电压和相同温度下比较每个eFPGA。您应该期望来自eFPGA供应商的软件工具将允许您检查不同工艺转角和电压组合下的性能。

请注意,您的RTL适用于eFPGA。如果从硬连线ASIC设计中采用RTL,则触发器之间往往会有20~30个逻辑层。如果你把它放在没有优化的eFPGA中,它会运行得非常慢。在eFPGA中,LUT输出总是有触发器,您可以使用它们向RTL添加更多的流水线,以在eFPGA中获得更高的性能。

谈到RTL,确保你正在测试什么对你很重要。

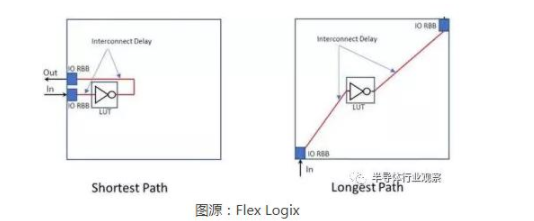

一个16位加法器。你关心的是它的运行速度有多快,但是如果你不小心,看到的结果可能会让你感到惊讶。现在想象一个大的eFPGA。如果加法器放置在阵列的一个角落,输入和输出接近,则性能将远高于在阵列中间找到加法器的情况。这是因为如果您观察从阵列输入到阵列输出的性能,当加法器位于阵列中间时,到数据输入和加法器输出的加法器的距离会更长。实际上,加法器是相同的,并且在两个位置运行速度都很快。问题在于你的测试没有隔离加法器的性能,但它也加入了达到加法器所需的信号。

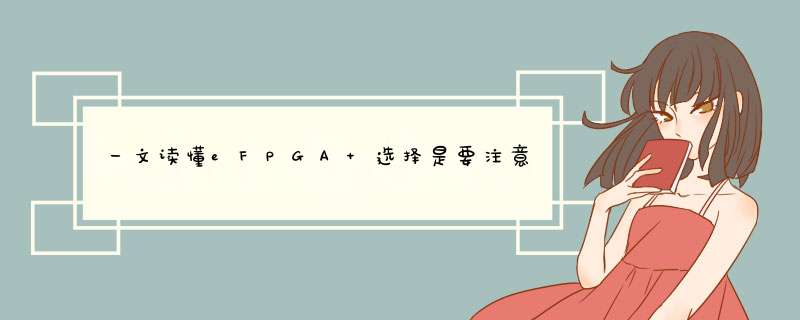

下图是一个例子,它使用一个LUT来布线,LUT速度不会改变,但通过互连进入和离开LUT的延迟会发生。

为了应对这种效应,尤其是因为您可能会比较两种不同尺寸的eFPGA,您需要做的是在输入和输出上设置寄存器,这可确保您关心的性能均可测量,不受阵列的大小和位置的限制。

如果您需要MAC的DSP或AI功能,请了解每个eFPGA的乘法器大小和流水线的不同。 如果RTL指定了一个MxN乘法器,那么综合软件将确保eFPGA实现它,但它可能会跨越两个或更多乘法器以达到所需的效果。 如果你需要MxN,那么这很重要。 但是,如果试图比较apples-to-apples的倍增性能,您会希望让RTL使用适合您所评估的所有eFPGA的倍增器大小。

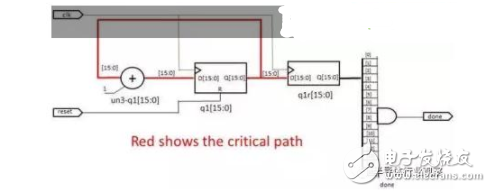

一些eFPGA直接将MAC汇集到一起,这比可编程互联网络快得多。 实施N-Tap FIR滤波器将显示具有MAC-to-MAC流水线的eFPGA与不具有流水线的eFPGA之间的差异。 上图为使用流水线DSP MAC实现的N-Tap FIR滤波器的示例。

步骤4:使用您需要的RTL基准测试区域

与性能一样,在尝试针对不同eFPGA的RTL的相对面积进行基准测试时,要非常小心。一些eFPGA供应商使您能够轻松生成数十种不同的阵列尺寸,但其他人可能只会为您的基准测试提供两种尺寸。

第一步是查看LUT计数(或MAC计数)。但是,不同的eFPGA供应商可能有不同的LUT尺寸。在查找表中可能不会填满它,所以如果你有两个触发器进入一个与非门,再进入另一个触发器,那么任何大小的查找表都将实现一个与非门。

某些eFPGA在输出端具有两个触发器,这使得N输入LUT可以分解为两个共享N输入LUT和一些输入子集的更小的LUT。此功能可提高面积利用率。

即使您正在对来自两家供应商的N-LUT eFPGA进行基准测试 - 并且您的设计使用了两个LUT中的一半并且两者的面积相同 - 但您不能断定它们同样好。 你需要确定的是eFPGA LUT的利用率是否可以实现。一般eFPGA的利用率为60-70%,但有些eFPGA的利用率可达到90%。 唯一能找到的方法是使RTL几乎填满eFPGA的LUT。

另一种获得使用感的方法是查看展示位置的可视化。 在下面的例子中,LUT显然是非常紧密地组合在一起的(阴影块是设计中使用的LUT),这是高利用率的良好视觉指示。

但是,即使在这里你也必须小心。 如果在上面的设计中,输入和输出均匀分布在eFPGA阵列的边上,那么随着位置/路径软件将关键路径最小化,将具有更均匀地分散LUT的效果。

因此,当使用这种可视检查时,尝试将输入和输出分组到eFPGA的一个角落,这样,位置/路线软件就可以将LUT放在一起,以最小化关键路径。

步骤5:对输入和输出容量进行基准测试

一些基于eFPGA的应用程序需要大量的输入和输出。例如,网络芯片的总线可以是512位宽(有时甚至数千位宽)。 您需要查看每个K-LUT可用的输入和输出计数,看看它是否在满足您需求的范围内。

结论eFPGA是令人兴奋的新工具,它使SoC架构师可以使他们的芯片更加灵活和可重新配置。

使用上面的指导原则,您将能够更快地找到最适合您独特应用程序、特定需求的eFPGA。如果您选择正确的解决方案,您将能够充分发挥eFPGA的潜力。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)