现在我们对比一下CPLD和FPGA的主要特性,提供一个简单参考,帮助确定某一设计适合采用哪类器件。

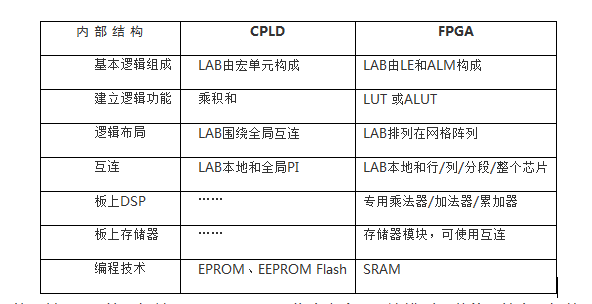

首先,对比一下硬件,如表1.2所示。

表1.2 FPGA与CPLD的硬件对比

PLD和FPGA都是由逻辑阵列模块构成的,但是CPLD LAB基于乘积和宏单元,而FPGA LAB使用基于LUT的逻辑单元。CPLD LAB围绕中心全局互连排列,随着器件中逻辑数量的增加,呈指数增长。

FPGA LAB以网格阵列排列,随器件密度线性增长。CPLD互连包括LAB本地可编程阵列及中心可编程互连。FPGA器件包括本地互连,用于各个LAB,但是和LAB逻辑分开,器件还包括行列互连,这些互连跨过阵列中的多个LAB,以及整个芯片的长宽。

FPGA器件一般包括专用资源模块用于存储或者DSP逻辑。CPLD不含有这些资源。最后,CPLD包括片内EPROM、EEPROM或者闪存结构,以存储编程和配置信息,这些信息在断电后也不会丢失。FPGA使用SRAM单元进行编程,这种易失编程技术要求器件每次上电时都进行编程。

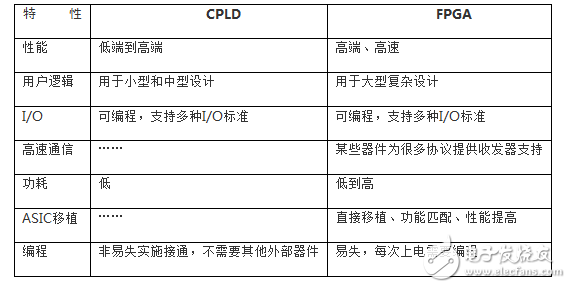

对基本特性进行对比,是选择使用哪种技术最好的方法。CPLD性能合适,而FPGA速率更高。这两种技术都能够为复杂功能设计提供大量的逻辑。但是,FPGA由于具有LAB网格阵列,逻辑资源更丰富。对于高速通信应用,唯一的选择是使用某些FPGA中的收发器。

一般而言,CPLD的功耗较低,但是FPGA也有很多低功耗特性,其功耗几乎和CPLD相当,具体取决于设计。当把设计移植到固定的结构化ASIC时,唯一选择是使用FPGA。最后,设计电路板时,必须考虑FPGA编程需要的外部元件,占用的电路板面积、电路板走线和功耗等。CPLD是单机器件,在编程和正常工作时,不需要任何额外的硬件。选择可编程逻辑器件时需要考虑很多选项和因素。

在选择器件时,进行对比是良好的开始,但还是需要经常查看器件手册,以了解器件特性和不足。如表1.3所示,是CPLD和FPGA的特性对比。

表1.3 CPLD和FPGA的特性对比

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)