CPLD相对于老的PLD器件的最大进步在于它能够在单个器件中容纳大量的逻辑。理论上,可以不断在CPLD中加入LAB,继续增加逻辑数量。但是,这样做需要有额外的PI布线,实现所有这些LAB的连接,其连接数量会呈指数增长,直到芯片管芯的连线数量超过逻辑数量,这限制了容量的扩展。

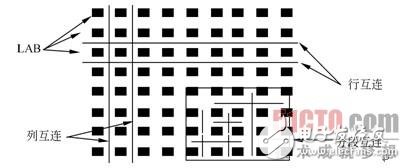

解决方法是把LAB排列在网格中,从而产生了现场可编程门阵列FPGA的概念,LAB都被排列在大型阵列中,器件可以现场编程或者重新编程,和CPLD一样。没有采用中心全局器件互连,而是把布线放置在LAB之间的空格上,就像大城市的街道。这种布线被排列成行列互连的形式。它可以跨过器件的整个长度和宽度,或者器件的一小部分,只覆盖行列中的几个LAB,如图1.9所示。

图1.9 FPGA互连结构图

FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即LE,而且本地互连和逻辑分开。LE看起来可能和CPLD宏单元相似,但更容易配置,有更丰富的特性来提高性能,减少逻辑资源的浪费。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)