PAL之后是PLD,PLD和PAL器件非常相似,但是加入了一些其他特性,成为真正的可编程器件,而且更实用。该器件区别于简单PAL器件的主要进步是它含有全面可编程宏单元,以及可变乘积项分配。

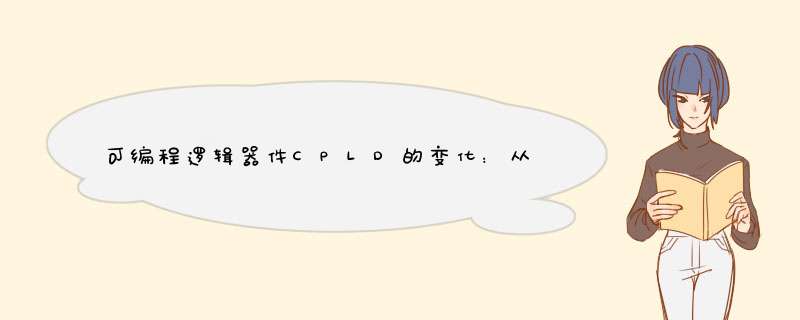

宏单元提供多种可编程选择,实现乘积和输出。可编程宏单元还能够反馈至阵列或者使用输出引脚作为输入。灵活的PLD宏单元成为实现逻辑功能真正实用的器件,第一款PLD如图1.6所示。

图1.6 第一款PLD示意图

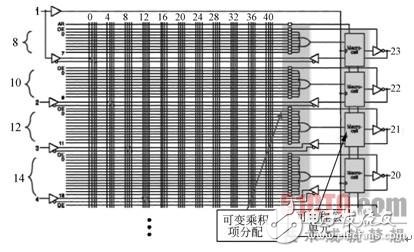

图1.7 CPLD结构图

CPLD中的逻辑模块通常被称为逻辑阵列模块(LAB),每个LAB就像一个PLD。CPLD LAB一般含有4到20个宏单元。LAB中的可编程阵列非常类似于PAL或者PLD阵列。

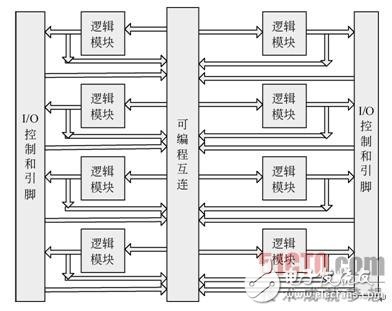

然而,CPLD和PLD中的可变乘积项分配不同,CPLD LAB中的宏单元通常包括额外的与门逻辑,这些逻辑直接反馈回阵列。这一额外的逻辑可用于形成额外的乘积项,名为扩展项。扩展逻辑产生的额外乘积项可用于当前的宏单元中,以扩展逻辑功能。

其他宏单元还可以共享使用扩展项。这样,对于需要乘积项的宏单元而言,只建立一次乘积项即可,而不必每次都建立。这是减少逻辑浪费更高效的方法,如图1.8所示。

图1.8 CPLD LAB中的宏单元

注意:使用扩展项逻辑的缺点是由扩展乘积项导致的额外时延,而使用扩展项逻辑的时延是已知的。因此,放置逻辑和进行时序分析时,应对此进行考虑。

除了LAB,CPLD中的其他结构与PAL和PLD相似,但配置更高级。LAB之间的互连被称为可编程互连阵列,即PI或者PIA。PI与PAL和PLD中的可编程阵列相似,使用了相同的编程技术。而PI提供了LAB之间以及LAB和I/O引脚之间数据传送需要的所有走线。

通过PI,任何LAB的输入和输出都可以连接至任一其他LAB或者I/O。这是实现非常灵活的可编程器件的关键。CPLD相对于PLD的另一改进是加入了单独的I/O控制模块。在PLD中,I/O引脚直接连接至逻辑。在CPLD中,PI将I/O引脚和器件的主要逻辑分开。I/O引脚有自己的控制逻辑来实现多种特性,任一引脚有多种I/O标准,输入、输出,或者双向工作,并不需要迫使某些引脚只能用做输入。

CPLD相对于PLD最大的优点在于逻辑数量及布线选择。LAB逻辑和PI是全面可编程的,在单片器件中具有很大的设计灵活性。CPLD的I/O特性和功能远远超出了PLD的简单I/O,在I/O怎样工作上提供更多的选项和控制功能。

与PAL和PLD一样,CPLD在电路板上电时即可瞬时接通工作。它们具有很低的成本,占用了很少的电路板面积。非易失EEPROM编程体系结构使其非常适合使用在系统编程方法进行测试和调试,不需要在电路板上电时对其进行重新编程。目前的Altera CPLD包括MAX 3000和7000系列器件,以及MAX II和MAX IIZ系列。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)