由于在传统的FPGA中增加了处理器,在ASIC中增加了可编程性,使得这些产品的界限越来越模糊了。

FPGA与以前的自己相比,现在都是摇滚明星了。不再只是一个查找表(LUT)和寄存器的集合,FPGA已经远远超出了现在的系统体系结构和原来只是用于证明未来ASIC设计架构的工具。

FPGA器件系列现在包括了从基本的可编程逻辑到复杂的SoC器件。在各种应用领域,汽车和其他应用领域的人工智能、企业网络、航空航天、国防和工业自动化等等,FPGA使芯片制造商能够在需要时随时更新系统。在新的市场中,这种灵活性至关重要,协议、标准和最佳案例仍在不断发展,ECOs需要保持竞争力。

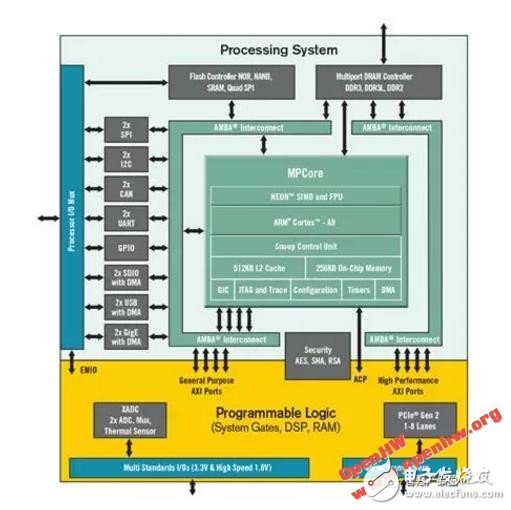

这就是赛灵思(Xilinx)公司的决策理由,Xilinx在它的Zynq FPGA里增加了一个ARM核处理器,以打造一个SoC FPGA芯片。Aldec公司的营销总监Louie de Luna说,“最重要的是,供应商已经改善了他们的工具流程。这使得他们对Zynq更感兴趣。他们的SDSoC开发环境看起来像C,这对开发人员很有好处,因为应用程序通常是用C编写的。因此,他们输入软件功能,并允许用户将这些功能分配给硬件。”

图:赛灵思的Zynq-7000 SoC(来源:Xilinx)

这些不仅仅是SoC FPGA,这也是他们有自主专利的SoC。

“它们可能包含若干个嵌入式处理器、专用计算引擎、复杂接口、大的内存等等,” OneSpin SoluTIons的产品综合验证专家Muhammad Khan说。“系统架构师计划和使用FPGA的可用资源,就像他们做一个ASIC那样。设计团队使用综合工具将他们的SystemVerilog、VHDL或SystemC RTL代码映射到基本逻辑元件中。对于设计过程的大部分,在有效针对FPGA和针对ASIC或全定制芯片之间的差异正在减小。”

ArterisIP的首席技术官Ty Garibay非常熟悉这种演变。“从历史上看,Xilinx从2010开始形成Zynq路径。他们定义了一种产品,它基本上是把一个ARM SoC的硬宏嵌入到现有FPGA里,”他说。“后来Altera雇我基本上做同样的事情。价值命题是SoC子系统是许多客户想要的东西,但由于SoC的性质,特别是处理器,他们不适合综合到一个FPGA。嵌入到实际可编程逻辑的功能级是令人望而却步的,因为它几乎使用了整个FPGA的资源。但它可以作为一个硬件功能只占FPGA很小的资源。你放弃了为SoC提供真正可重构逻辑的能力,但它是可编程的软件,因此它是以这样的方式来改变功能。”

这意味着可以实现一个软件可编程,一个硬宏,然后在构架中实现硬件可编程功能,他们可以一起工作,他说。“有一些很好的市场,尤其是在低成本汽车控制的地方,过去传统做法是在FPGA旁边放一个中等性能的微控制器。客户只会说,‘我只要把整个功能放到FPGA芯片的硬宏上,以减少电路板空间,减少BOM,降低功率。’”

“FPGA供应商一直不断在培育芯片,但也增加了越来越多的硬件逻辑,因为有一个很大比例的客户群需求,”Garibay说。“今天发生的事情是把它扩展到软件可编程那一面,在ARM SoC之前我们添加的大部分东西都是不同形式的硬件,主要与I/O有关,但我们也有必要尝试通过加强可编程逻辑门来加固像DSP这样的东西,因为市场有足够的应用需求。”

01

市场视角

这样做实质上已经把FPGA变成了像设计瑞士军刀一样的多可能性。

“如果倒转时间,它只是一堆LUTs和寄存器,而不是门,”NetSpeed Systems的市场营销和业务发展副总裁Anush Mohandass说。“这里有一个经典的问题,如果你使用通用版本,并将其与特定于专用程序的版本进行比较,通用计算将给出更多的灵活性,而专用的版本会比通用版本在性能或效率上更优。Xilinx和Altera正试图越来越多将这两块结合,他们注意到每个FPGA客户都有诸如DSP或某种形式的计算需求。因此,他们嵌入ARM核,嵌入DSP核,他们嵌入所有不同的PHYs(物理结构)和常用的东西。并固化它,使它更有效,同时性能指标也变得更好。”

这些新的能力为FPGA在各种新的和现有市场中扮演重要角色打开了大门。

“从市场的角度看,FPGA肯定会进入SoC的市场,”新思科技高级营销总监Piyush SancheTI说。“不管你做FPGA还是做十分成熟的ASIC,都有一个经济学问题。现在这些路线开始变得模糊,我们看到越来越多的公司,特别是在某些市场上,反而做FPGA产品的生产会取得较好的经济效益。”

从历史上看,FPGA曾被用于原型设计,但是对于生产使用来说,它仅限于像航空航天、国防和通信基础设施这样的市场,SancheTI说。“现在这个市场正在扩展到汽车、工业自动化和医疗电子。”

02

AI:FPGA的一个新兴市场

那些信奉FPGA的公司一般都是系统供应商/ OEM,他们总是希望优化自己的IP或AI/ML算法的性能。

“他们想建立自己的芯片,对于很多人来说,开始做ASIC可能会有点吓人,” NetSpeed的Mohandass说。“对于不想花3000万美元的晶圆成本来制造芯片的他们来说,FPGA是一个有效的切入点,在那里他们有计划中的独特算法,独特的神经网络,用FPGA设计看看是否可以得到他们正在寻找的功能。”

目前人工智能应用面临的挑战是量化,西门子业务Mentor的Catapult HLS综合验证高级产品营销经理Stuart Clubb说。“我们需要什么样的网络,该如何建设那个网络,内存结构是什么?你从网络开始设计,即使只有几层,有很多数据在若干个系数中,它很快地旋转到几百万个系数,内存带宽变得非常可怕。没有人知道什么架构可行,如果答案是未知的,你就不会跳进去贸然建立一个ASIC。”

在企业网络领域,最常见的问题是加密标准似乎一直在变化。“把加密设计到FPGA里代替设计一个ASIC,对加密引擎更好,”Mohandass说。“或者,如果你在全球网络方面做任何类型的数据包处理,FPGA仍然给会你更多的灵活性和可编程性。这就是灵活性发挥作用的地方,他们也利用了这一点。你仍然可以称之为异构计算,它看起来更像一个SoC。”

03

新规则

随着新一代的FPGA SoC,旧的规则不再适用。具体来说,如果你在板子上调试,那你就错了,”Clubb指出。“虽然在板上调试被认为是一种低成本的解决方案,这可以追溯到能够说“可编程”的早期阶段。但如果现在说,‘我发现一个bug,我可以修复它,在一天之内编程一个新的比特流,然后把它放回板子上,再找到下一个bug,’那就是疯了。这是一种被视为不关心成本的心态,就像你在做普通员工那样,管理层不会购买模拟器、系统级工具或调试器,因为‘我只是付钱给那个家伙完成任务,我会对他大喊大叫,直到他更努力工作。’”

这种行为仍然很普遍,因为有足够多的公司,他们每年都会把底部10%的员工砍掉以让每个人都保持警觉的态度,他说。

然而,FPGA SoC是真正的SoC,需要相同的严格设计和验证方法。“事实上,可编程的构造并不真正影响设计和验证,”Clubb说。“如果你做一个SoC,例如,你可以做我听到的一些客户称之为“乐高”工程,这是一个框图法。我需要一个处理器,一个内存,一个GPU,一些其他的小模块,一个DMA内存控制器,WiFi,USB和PCI。这些都是你组装的‘乐高’块。麻烦的是,你必须确认他们能工作,并且能在一起工作。”

尽管如此,FPGA SoC系统开发人员还是很快赶上了他们的SoC兄弟们,在那里,验证方法是值得关注的。

“它们不是像原先的传统硅SoC开发商那样的心态:‘这将花费我200万美元,所以我最好把它弄对。’因为FPGA的失败成本很低,”Clubb说。“但是如果你花了200万美元开发FPGA,你弄错了,现在你要花三个月来修复bug,还有一些其他问题需要解决。需要组建多大的团队,要花多少钱,产品上市时间的处罚成本,市场在哪里等等?这些都是很难明确量化的成本。如果你是在一个消费领域,几乎不太可能去考虑用FPGA,你真正关心的是它能不能赶上圣诞节前上市,所以有一点不同的优先级。考虑定制硅中做SoC的总成本和风险,当你扣动扳机说:‘这是我的系统,我已经完成了,’其实你看不到那么多。我们知道,这个行业正在整合,很少有大玩家做大筹码。每个人都想办法来做,而这些正是FPGA可以提供的。”

04

新的折衷方案

工程团队设计目标器件时常常会有意留出一些选项,这并不少见。SancheTI说,“我们看到很多公司创建RTL并验证它,几乎不知道是去做FPGA还是做ASIC,因为很多因素可以让这个决定改变。你可以从FPGA开始,如果达到了某个量,从经济学角度考虑可能你会去做一个ASIC。”

这尤其适用于今天的人工智能应用领域。

“已经有一系列技术被用于人工智能算法加速,”eSilicon市场营销副总裁Mike Gianfagna说。“显然,AI算法已经存在很长时间了,但是现在我们突然碰到更加复杂的情况是如何使用它们,颇堪称奇的是在近乎实时的速度下运行它们的能力。它从CPU开始,然后转移到GPU。即使GPU是一个可编程的通用器件,一个就可以适合所有。虽然架构擅长并行处理,因为这就是图形加速的全部内容,这很方便,这就是AI的全部内容。在很大程度上它是好用的,但它仍然是一种通用的方法。这样你就可以得到一定程度的性能和功率的覆盖。一些人接下来要转移到FPGA,因为这比你用GPU可以更好地设计电路,并在性能和功率效率方面取得进步。ASIC对功率和性能来说是终极的,因为在那里你有一个完全定制的架构,它能满足你所需要的,不多也不少。这显然是最好的。”

人工智能算法很难映射到硅中,因为硅处于几乎不变的状态。所以在这一点上做一个全定制的ASIC不是一个好的选择,因为相对硅的时代它已经过时了。“FPGA是很好的选择,因为你可以重新编程它们,所以在昂贵芯片上的投资也不会损失。” Gianfagna说。

这里,有一些自定义内存配置,以及某些子系统功能,如卷积和转置存储器,它们被再次使用。因此,当算法可能改变时,有一些模块不会被改变/或被反复使用。他补充说。考虑到这一点,ESILICON正在开发一个带有软件分析的平台来研究人工智能算法,目标是能够更快地为特定的应用选择最佳的体系结构。

“FPGA为你提供了更换机器或发动机的灵活性,因为你可能会遇到一种新的网络,提交ASIC是有风险的,因为你没有最好的支持,以及这样的灵活性,”,eSilicon IP工程副总裁Deepak Sabharwal说。“然而,FPGA总是会在容量和性能上受到限制,所以你将无法真正达到FPGA的生产水平规格。你可以玩它和归类东西,但最终你可能不得不建立一个ASIC。”

05

嵌入式LUTs

另一个在过去几年取得了立足点的选择是嵌入式FPGA,它将可编程性构建为ASIC,而不是将ASIC的性能和功率优势添加到FPGA中。

“FPGA SoC仍然主要是FPGA,具有相对少量的芯片面积用于加工,”Flex Logix首席执行官Geoff Tate说。“从框图看不出规模,要看实际芯片的照片,主要面积还是FPGA。但是有一类应用程序和客户,FPGA逻辑和SoC的部分之间的正确比率是更小的FPGA,他们的RTL编程在一个更具成本效益的芯片尺寸上。”

这种方法在航空航天、无线基站、电信、网络、汽车和视觉处理领域,尤其是人工智能领域找到了牵引力。“算法变化如此之快,以至于芯片在返回时几乎就过时了”Tate说。“使用一些嵌入式FPGA,可以让他们更快地进行算法迭代。”

从人驾驶汽车转向自动驾驶汽车,这一点尤其明显。虽然失效和老化的问题得到了很多关注,但挑战是如何保持“优雅的退化”。根据Achronix系统工程副总裁Raymond Nijssen的说法,“性能和质量随着时间的推移而变化,标准也是如此。对汽车识别一个孩子过街的要求是相对较新的。没有人知道规章会如何改变,或者你如何测试。但你如何测试还不知道的标准呢?”

在这种情况下,可编程性对于避免重做整个芯片或模块就变得至关重要,Nijssen说。

06

设计调试

尽管这只是一部分原因,与所有的SoC一样,了解如何调试这些系统,并在仪器中构建,可以帮助它们在成为主要问题之前识别它们。

“随着系统FPGA变得更像SoC,他们需要适用于在SoC中的开发和调试方法,”UltraSoC的首席执行官Rupert Baines说。“有一个(也许是天真的)信念,因为在FPGA上你可以看到所有东西,调试起来一定很容易。这在比特级别上是正确的,带有波形观察器,但是当到达系统级时它不成立。最新的大型FPGA显然是系统级的。在这一点上,你从一个探针排列得到的波形图并不是非常有用。你需要一个逻辑分析器,一个协议分析器,以及处理器内核本身的良好的调试和跟踪能力。”

FPGA的大小和复杂性要求与ASIC类似的验证过程。基于测试台的复杂的UVM支持模拟,通常也支持仿真。正规的工具都在这里扮演着重要的角色,从自动设计检查,到权威验证以及一系列强大的解决方案。虽然FPGA可以比ASIC更快速、更便宜地改变,这是事实,在大型SoC中检测和诊断BUG的困难意味着在进入实验室之前必须对它们进行彻底的验证,OneSpin的Khan说。

事实上,在一个领域中,对FPGA SoC的验证要求比在RTL输入和后综合网表之间的ASIC等价性检查更高。FPGA的阐述、综合和优化阶段常常比传统的ASIC逻辑综合流程对设计有更多的修改。这些变化可以包括跨越循环边界的移动逻辑,以及在存储器结构中实现寄存器。彻底的时序电路等价性检查对于确保最终的FPGA设计仍然符合RTL中的原始设计者意图是必不可少的,Khan补充说。

在工具方面,也有优化性能的空间。“使用嵌入式视觉应用程序,其中很多都是为Zynq编写的,每秒钟可以获得5帧图像。但如果你用硬件加速,就可以得到每秒25-30帧,这为新型器件铺平了道路。问题是,这些器件的仿真和验证并不简单。你需要在软件和硬件之间进行集成,这是困难的。如果你在SoC运行所有的东西,那太慢了。它可以模拟5到7个小时,如果你用协同仿真,就可以大大节省模拟时间,” Aldec’s de Luna说。

简单地说,在复杂的ASIC中使用的相同类型的方法现在正在用于复杂的FPGA中。随着这些器件在功能安全性应用中的使用,这一点变得越来越重要。

“这就是为了确保有故障传播路径,然后验证这些路径的形式化分析,” Cadence的集团营销总监Adam Sherer说。“这些东西都是非常适合形式化分析。FPGA验证的传统方法是无法完成这类验证任务的。它在FPGA设计中仍然很普遍,假设它非常快,很容易达到以系统速度运行的硬件测试。即使它运行在系统速度,一个非常简单的模拟就能完成一个全面的检查。然后你编程这些器件,在实验室开始启动运行。除了实验室中的可观测性和可控性是极其有限的,这是一个相对快速的路径。因为只有在从FPGA的内部拉动数据到引脚才能进行探测,这样才能在测试仪上看到它们。”

Breker验证系统公司的首席营销官Dave Kelf同意这一点,“这使得器件验证的方式发生了有趣的转变。在过去,通过将设计加载到FPGA本身并在测试卡上实时运行的方法使较小的器件尽可能多地验证。随着SoC和软件驱动设计的出现,可以预期这种自我“原型”的验证方式可能与软件驱动的技术结合得很好,对于这个过程的某些阶段,它确实如此。然而,在原型开发过程中识别问题并调试它们是很复杂的。这种较早的验证阶段需要进行仿真,因此SoC风格的FPGA看起来越来越像一个ASIC。考虑到这两个过程,它们之间的协同使得过程更加高效,包括常见的调试和测试平台。新的进展,如便携式激励(Portable Stimulus)会提供这种协同性,事实上,使得SoC FPGA更易于管理了。”

07

结论

Sherer说,展望未来,用户正在寻求把那种在ASIC世界更严格的工艺整合到FPGA。

“有大量的培训和分析,他们希望在FPGA中有更多的技术用于调试,以获得这样的支持。”他说。“FPGA社区倾向于落后于现有技术,倾向于使用非常传统的方法。因此,他们需要在空间、规划和管理、需求追溯等方面进行培训和培养意识。来自SoC流程的那些元素在FPGA中是绝对必要的,而FPGA本身并没有推动这个那么多,而是那些最终应用的工业标准在推动它。需要对在FPGA环境下工作的工程师进行再培训和再教育。”

在大量需要灵活性的应用驱动下,ASIC和FPGA之间的界限正变得模糊,系统架构越来越多地结合可编程性与硬件逻辑,以及工具,这些现在都适用于两者。这种趋势不太可能很快改变,因为许多新应用领域要求的这些组合仍然还处于萌芽阶段。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)