利用4个dsp48e1模块,实现四路加法器,dsp48e1模块在手册中表示比较复杂,找了两个图,可以大致看懂他的基本功能。

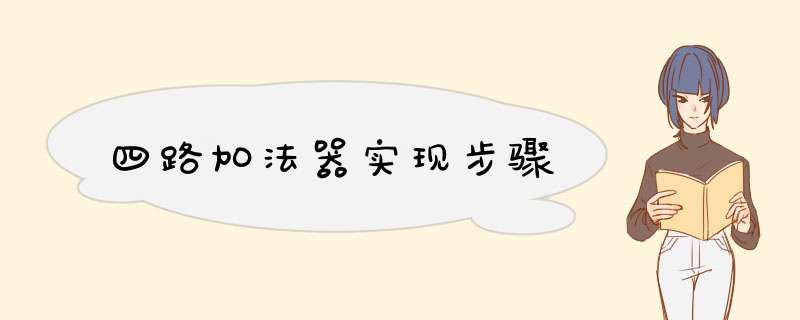

图1 dsp48e1端口说明

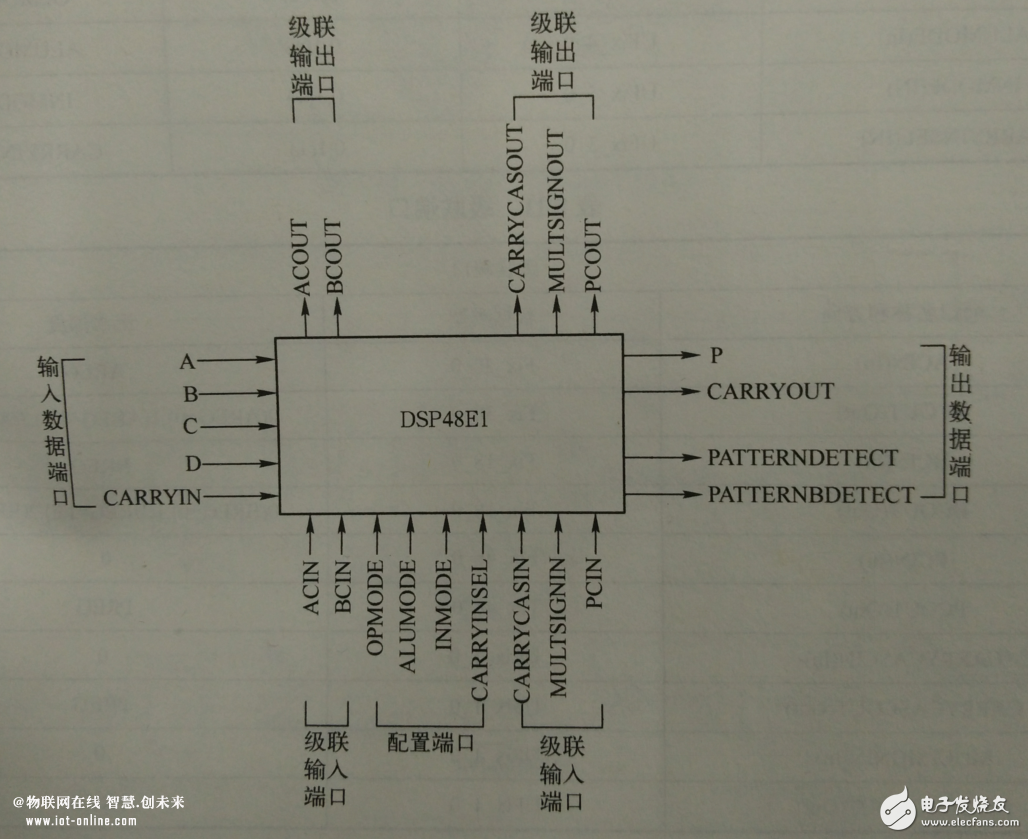

图2 简化的DSP48E1结构

软件环境 Matlab 2014 a

Vivado 2014.4

System generator 2014.4

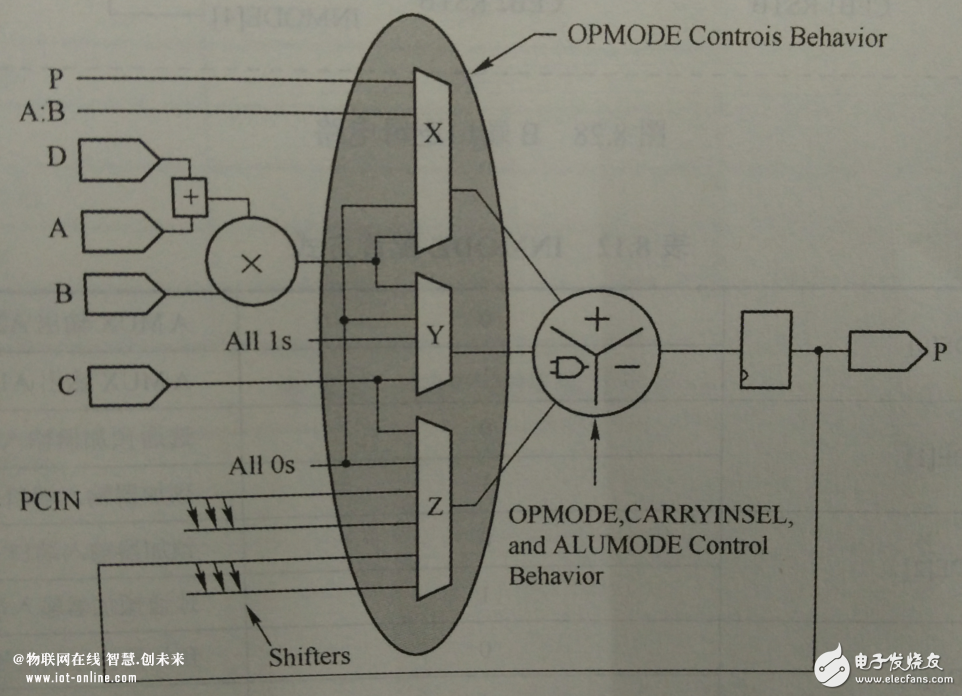

实现步骤1、 模型搭建与仿真

在simulink环境下工程搭建如下

图3 四路加法器原理图

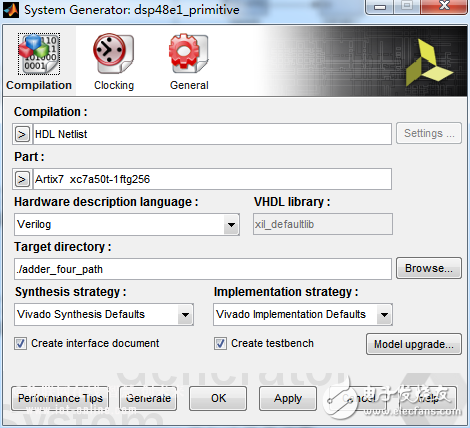

模型搭建完毕后,双击system generator ,按照a7试用板的型号设置如下

图4 system generator

2、vivado仿真

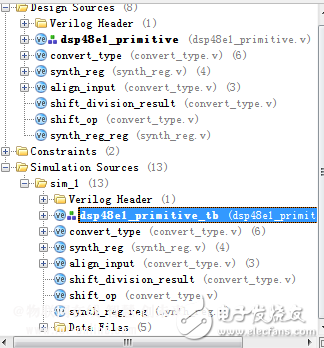

找到输出目录,打开xpr文件,可得完整的vivado工程

图5 工程结构

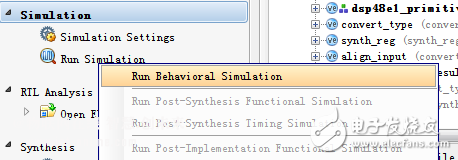

直接运行仿真

图6 仿真

仿真结果

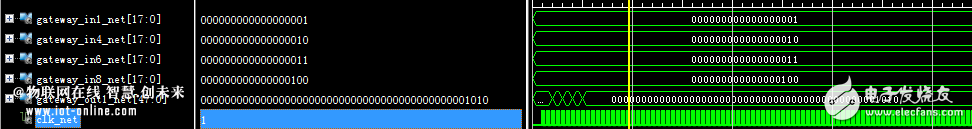

设置4路输入,分别输入: 1,2,3,4(fix_18_0),可得48bit的输出1010b

图7 仿真结果

分析还没有用到SIMD功能,不知道为什么,一旦勾选SIMD功能将48bit拆分成4个12bit就会出现报错,可能是我的参数设置有问题,这一步还得继续看一下官方的手册,希望下次能够将这个问题解决。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)