1 ARM 系统及IDE 接口综述

ARM (A dvanced RS IC M ach ines) 是一种低功耗、高性能的32 位处理器。本文介绍的系统是基于Sam sung 公司S3C44B0X 构建而成。该CPU 的内核是ARM 7TDM I, 采用了三级流水线和VON N eumann 结构, 并且具有UART、IIC、IIS、S IO 接口,ADC、PWM 通道, 实时时钟、LCD 控制器等。

硬盘接口结构主要分I/O 控制层和逻辑映射层。其中I/O 控制层包括与ARM 的物理接口, 实现对硬盘状态的查询、设置和对扇区的读写。它是依据A TA 标准连接的IDE 接口。通过IDE 接口选择可编程的P IO 或使用DMA 方法传输数据。本文将介绍P IO 方式传送, 即对硬盘每一次访问都需要分别进行编程.

逻辑映射层实现对目录、文件与扇区数据逻辑映射, 以及数据的存储和修改。该部分应用微软公司FA T 标准, 为每个文件的磁盘块构造链接表, 通过链接表和它的索引实现对整个磁盘文件进行管理。

在微机应用中, 由于常涉及大批量数据的存储,在联网条件不备的情况下, 通过IDE 接口连接大容量硬盘是一个有效方法。若按照AN S I 的A TA 标准连接硬盘, 并通过Fat32 文件系统进行数据管理,嵌入式系统读写过的硬盘, 还可以脱机移到W in2dow s *** 作系统支持下的PC 机中, 实现与常规 *** 作系统共享硬盘数据资源。本文介绍的方法可以推广到其它微处理器应用系统中。

2 硬件结构与I/O 控制层

A TA 标准对IDE 硬盘接口作了详细描述。

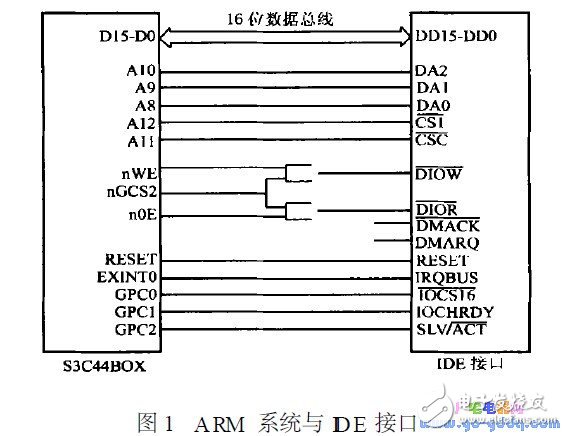

图1 是按照A TA 规范结合P IO 传输特点进行连接。由于没有使用DMA 传输方式, 故DMARQ 和DMACK 两根悬空; / IOCS16 用于选择使用DD0~DD15 进行16 位传输或使用DD0~DD7 进行8 位传输; /D IOR 和/D IOW 是对磁盘驱动寄存器进行读写 *** 作的一对握手信号; /C S0 用来选定命令寄存器组, /C S1 选择控制寄存器组。这两根信号线结合DA 0~DA 2, 就可以对IDE 多个寄存器进行访问,如数据寄存器、状态寄存器、命令寄存器等。

此外,A TA 标准对IDE 命令也有严格定义, 如用来确认驱动器的0xEC, 读缓冲区的0xE4。在P IO模式中, 系统将IDE 命令送到命令寄存器中, 读写相应的数据、状态寄存器, 实现对硬盘访问和控制。

对硬盘内部数据的 *** 作需要了解它的物理存储方式。磁头、柱面和扇区是硬盘的基本结构, 而扇区是对硬盘读写的最小单位。硬盘内部的寻址方式有两种, 一种是物理寻址的CHS 方式, 另一种是逻辑寻址的LBA 方式。物理寻址CHS 方式是通过柱面、磁头和扇区号来确定唯一的存储单位, 较为繁琐。而逻辑寻址方式是采用线性映射方法, 从物理结构到逻辑块编号的映射关系如下:

LBA = (柱面编号×磁头数+ 磁头号) ×扇区数+ 扇区编号- 1

采用这种方法, 主机不用知道硬盘的物理结构, 就能直接对目标扇区进行寻址。

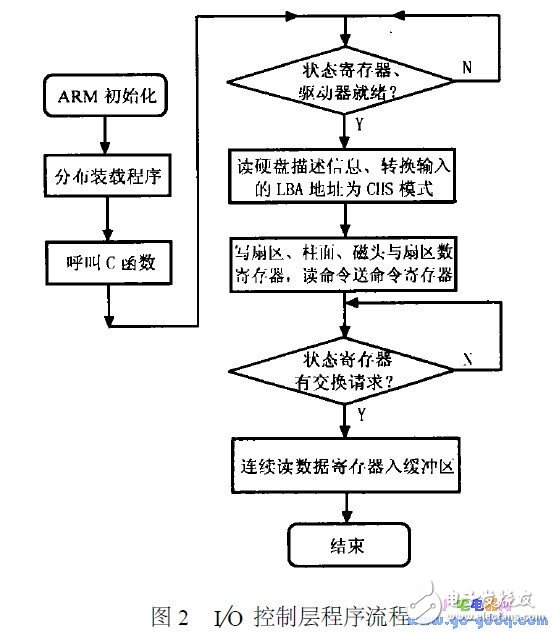

根据前面的阐述, 编制I/O 控制层的控制程序, 可对IDE 控制寄器进行查询、设置和逻辑寻址,实现对指定扇区的读写。图2 是读一个扇区数据的流程图, 写扇区的方法和它类似, 区别只是在于传送指令和数据流动方向不同。此外, 在检测状态寄存器的时候, 最好加上超时判断, 防止程序陷入死循环。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)