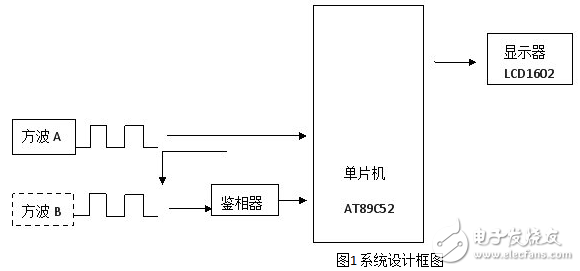

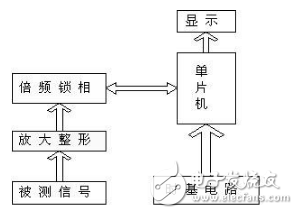

系统框图如图1所示,主要由AT89C52单片机、异或器件、LCD1602、电源等组成。

定时/计数器工作在方式1,每产生一次定时器0中断,计数65536个脉冲,此时的脉冲来自振荡器的12分频后的脉冲,其周期为1uS。根据产生外部中断0时,定时器0中断的次数u,以及此时定时/计数器0计数寄存器的数值X,即可求得待测方波的周期为:T=(65536*u+X)us,取其倒数即可求得待测方波的频率,小数点后保留两位,即可使得频率精度为0.1HZ。

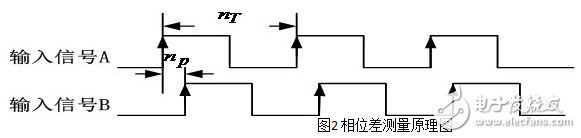

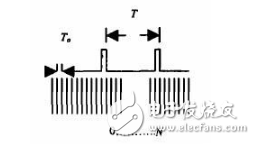

相位差的测量原理将两路同频不同相的方波信号进过鉴相器(即异或)后得到的脉冲宽度t与方波信号的周期T的比值(占空比),即对应为两信号的相位差,此时相位差

其中,脉冲宽度的测量方法与方波周期的测量方法相同。相位差测量的原理图如下:

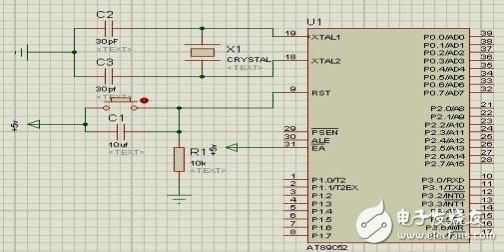

本设计中,P0端口(32~39脚)被定义为N1功能控制端口,分别与N1的相应功能管脚相连接。单片机正常工作时,都需要有一个时钟电路和一个复位电路。本设计中选择了内部时钟方式和按键电平复位电路,来构成单片机的最小电路。如图4所示。

图4 单片机最小系统

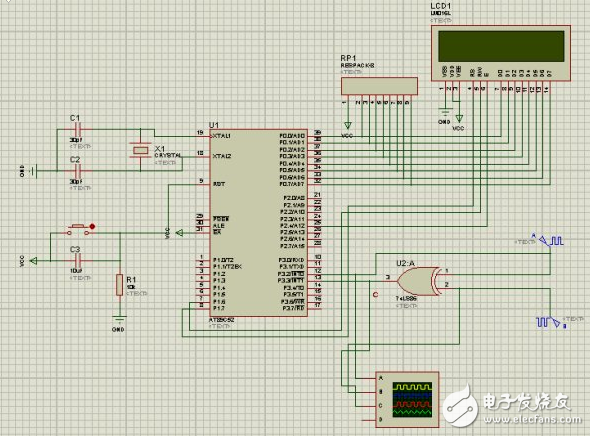

频率、相位表的总体电路图如图5所示:

图5 频率相位表的总体电路图

基于单片机简易数字频率计设计方案(二)本文利用前置分频器SAB6456A和高速数字分频器74HC390的分频功能,结合新型的MSP430F449单片机,给出了一种新颖的、全自动的数显测量射频频率的设计方案。

图1 信号的前端处理及分频电路

主要器件介绍MSP430F449单片机

MSP430F449 采用16位RISC结构,具有丰富的片内外设和大容量的片内工作寄存器和存储器,性能价格比很高。它的特点包括:

· 超低的功耗:能够在1.8V~ 3.6V的电压下工作;具有工作模式(AM)和5种低功耗模式(LPM)。在低功耗模式下,CPU可以被中断唤醒,响应时间小于6ps。

· 较强的运算能力:16位的RISC结构,丰富的寻址方式;具有16个中断源,可以任意嵌套;在8MHz时钟驱动下指令周期可达125ns; 内部包含硬件乘法器和大量寄存器,以及多达64KB的Flash程序空间和2KB的RAM,为存储数据和运算提供了保证。

· 丰富的片上外设:包括看门狗定时器,基本定时器,比较器,16位定时器(TA、TB),串口0、1,液晶显示驱动器,6个8位的I/O端口,12位ADC (最高采样率200kHz)等。丰富的片上外设可以很方便地构建一个较为完整的系统。另外,充分利用计数器的多路任意波形产生功能和中断控制功能,保证了一些复杂的时序控制任务的完成。

·方便高效的开发环境:MSP430F449是Flash型器件,片内有调试接口和电可擦写的Flash存储器,可以先下载程序到Flash内,再在器件内通过软件控制程序的运行,由JTAG接口读取片内信息供设计师调试。这种方式不需要仿真器和编程器,调试十分方便。

前置分频器SAB6456A

SAB6456A是专为UHF/VHF设计的前置分频器。内部的MCpin为分频控制端,可对频率范围为70MHz-1GHz的信号进行64/256分频,当MC pin开路时为64分频;当MC pin接地时为256分频。有较高的灵敏度和较强的谐波抑制能力。

图2 单片机外围电路

工作原理该设计主要分两部分:分频和计数。首先,输入信号限幅后经SAB6456A分频,256分频后的信号再经两片74HC390高速分频器进行1000分频,此时模拟信号变为低频数字信号,频率在10kHz以下;其次,分频后的信号直接接入MSP430F449单片机,利用内部的16位定时器A来定时和计数。该定时器可分为几个部分:计数器部分,捕获/比较寄存器及输出单元。其中,计数器有4种工作模式,3个捕获/比较寄存器。利用计数器的连续计数模式和上升沿捕获模式,在定时器中断中计数N个脉冲信号时间,再除N得到频率。

硬件设计图1为信号的前端处理及分频设计。输出后的信号再经两片SN74HC390分频,SN74HC390是高速分频器件,最高分频频率为50MHz。每片 SN74HC390可实现100分频,采用两片串联,可实现对信号的1000分频,经分频后的数字信号频率较低,约4kHz以下,可由单片机直接计数。

图2为单片机外围电路,包括复位电路,电源电路和单片机工作必须的晶振。晶振有8MHz和32.768kHz两种,8MHz 作为定时器A的计数器输入时钟源;32.768kHz 作为数码管的显示频率。74LS373为D型锁存器,5V单电源供电,因输出电流足够大,也可以直接驱动共阴极LG3631AH型数码管。

软件设计将分频的输出端OUT接至单片机的频率输入端,程序开始先延时一段时间,待信号稳定。开捕获中断和定时器A,在定时器A 中断中计数N个脉冲,测量结束后得到N个脉冲的时间,然后除N得到脉冲的频率,乘以分频系数得到实际频率并显示,经过短暂延时后重新测量,如此循环测量并显示。

在测量频率时,为保证精度要关掉LED显示,所以,对于频率较低的信号会发生LED闪烁的情况,解决办法是测量较少个脉冲以减少平均测量时间或减少延时。

采用动态扫描显示,动态扫描显示的原理是:由P4向各个位轮流输出扫描信号,使每一位瞬间只有一个数码管被选通,然后由P3向该位输入显示的字型码,驱动该位字形段显示字形。这样,在P3送出的码段和P4送出的位段的配合下,使各个数码管轮流显示各自的字形,每位的显示时间要超过1ms,这样人眼就感觉不到闪烁了。

测量主程序如下:

void frequency_measure(void)

{float tmp,tmp1;

key_flag=0;//按键标志清0

P1OUT|=BIT0;

Delay(1000); file://延时一段时间等待信号稳定

while(1)

{ IE2&=~0X80; file://关BT,关LED

firstflag=1;//开始测量第一个脉冲

TACTL|=TAIE; file://开捕获

CCTL1|=CCIE;//开TImer a

while (f_ok_flag==0);//等待测量结束

f_ok_flag=0;

if (aa1》aa2)

overflow=overflow-1;

tmp=aa2-aa1;

tmp1=40.0/(overflow*0.008191875+(tmp/8000000.0));

result=tmp1*0.256;

IE2|=0X80;//开BT,开LED

yanshi(2,2);//可以修改这里的参数,越大表示延时越长,太小的话LED就会变暗

CCTL1&=~CCIE;//关捕获

TACTL&=~TAIE;//关TImer a

return;

}

}

流程图如图3所示。

图3 主程序流程

结语本文给出的硬件和软件均经过实践检验,使用该测量仪器所测结果精度较高。该测量仪器价格较低,结构简单,是一种经济型的频率测试仪。

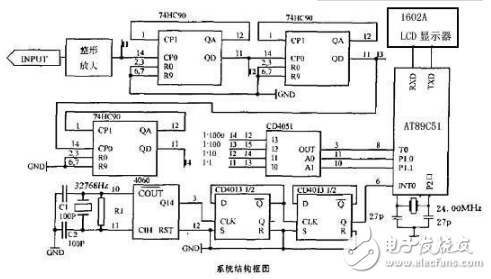

基于单片机简易数字频率计设计方案(三)本数字频率计将采用定时、计数的方法测量频率,采用一个1602A LCD显示器动态显示6位数。测量范围从1Hz—10kHz的正弦波、方波、三角波,时基宽度为1us,10us,100us,1ms。用单片机实现自动测量功能。

基本设计原理是直接用十进制数字显示被测信号频率的一种测量装置。它以测量周期的方法对正弦波、方波、三角波的频率进行自动的测量。

频率测量仪的设计思路与频率的计算频率测量仪的设计思路主要是:对信号分频,测量一个或几个被测量信号周期中已知标准频率信号的周期个数,进而测量出该信号频率的大小,其原理如右图1所示。

若被测量信号的周期为,分频数m1,分频后信号的周期为T,则:T=m1Tx 。由图可知: T=NTo

(注:To为标准信号的周期,所以T为分频后信号的周期,则可以算出被测量信号的频率f。)

由于单片机系统的标准频率比较稳定,而是系统标准信号频率的误差,通常情况下很小;而系统的量化误差小于1,所以由式T=NTo可知,频率测量的误差主要取决于N值的大小,N值越大,误差越小,测量的精度越高。

基本设计原理基本设计原理是直接用十进制数字显示被测信号频率的一种测量装置。它以测量周期的方法对正弦波、方波、三角波的频率进行自动的测量。

所谓“频率”,就是周期性信号在单位时间(1s)内变化的次数。若在一定时间间隔T内测得这个周期性信号的重复变化次数N,则其频率可表示为f=N/T。其中脉冲形成电路的作用是将被测信号变成脉冲信号,其重复频率等于被测频率fx。时间基准信号发生器提供标准的时间脉冲信号,若其周期为1s,则门控电路的输出信号持续时间亦准确地等于1s。闸门电路由标准秒信号进行控制,当秒信号来到时,闸门开通,被测脉冲信号通过闸门送到计数译码显示电路。秒信号结束时闸门关闭,计数器停止计数。由于计数器计得的脉冲数N是在1秒时间内的累计数,所以被测频率fx=NHz。

数字频率计(低频)的硬件结构设计系统硬件的构成

本频率计的数据采集系统主要元器件是单片机AT89C51,由它完成对待测信号频率的计数和结果显示等功能,外部还要有分频器、显示器等器件。可分为以下几个模块:放大整形模块、秒脉冲产生模块、换档模拟转换模块、单片机系统、LCD显示模块。各模块关系图如图2所示:

该系统工作的总原理图如图3所示:

图3 数字频率计系统工作原理图

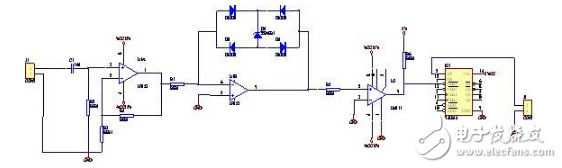

信号调理及放大整形模块

放大整形系统包括衰减器、跟随器、放大器、施密特触发器。它将正弦输入信号Vx整形成同频率方波Vo,幅值过大的被测信号经过分压器分压送入后级放大器,以避免波形失真。由运算放大器构成的射级跟随器起阻抗变换作用,使输入阻抗提高。同相输入的运算放大器的放大倍数为(R1+R2)/R1,改变R1的大小可以改变放大倍数。系统的整形电路由施密特触发器组成,整形后的方波送到闸门以便计数。

由于输入的信号幅度是不确定、可能很大也有可能很小,这样对于输入信号的测量就不方便了,过大可能会把器件烧毁,过小可能器件检测不到,所以在设计中采用了这个信号调理电路对输入的波形进行阻抗变换、放大限幅和整形,信号调理部分电路具体实现电路原理图和参数如下图4所示:

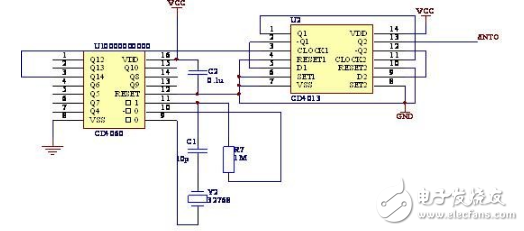

时基信号的产生原理:

本电路采用32768HZ晶体震荡器,利用CD4060芯片经过14级分频得到2HZ的信号(32768/214),在经过CD4013双D触发器经过二分频得到0.5HZ的方波,即输出秒脉冲信号使单片机进行计数。

图七 秒脉冲产生电路原理图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)