本文介绍了这种基于SRIO互联技术的高速实时数据处理硬件平台,并在该平台上研究了多DSP之间、DSP与FPGA之间的SRIO通信技术。

1 SRIO标准

RapiclI/O是面向嵌入式系统开发提出的高可靠、高性能、基于包交换的新一代高速互联技术,已于2004年被国际标准化组织(ISO)和国际电工协会(IEC)批准为ISO/IECDIS 18372标准。SRIO则是面向串行背板、DSP和相关串行数据平面连接应用的串行RapidIO接口。串行RapidIO包含一个3层结构的协议,即物理层、传输层、逻辑层。物理层定义电气特性、链路控制、低级错误管理;传输层定义包交换、路由和寻址机制;逻辑层定义总体协议和包格式。可以实现最低引脚数量,采用DMA传输,支持复杂的可扩展拓扑,多点传输;可选的1.25 Gbps、2.5 Gbps、3.125 Gbps三种速度能满足不同应用需求,是未来十几年中嵌入式系统互联的最佳选择之一。

2 基于C6455高速SRIO接口的互联系统

2.1 C6455的SRIO端口

2.2 基于SRIO的多C6455互联结构

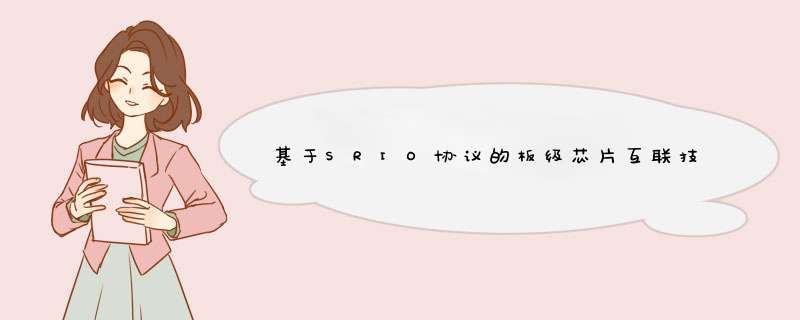

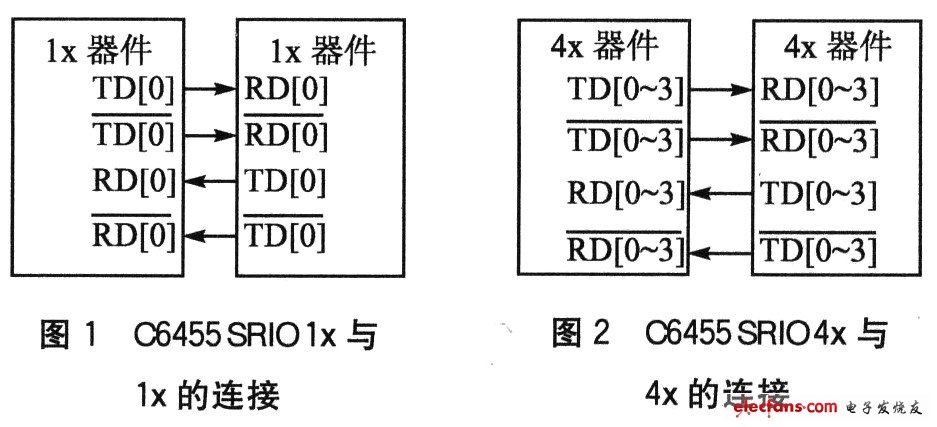

C6455的SRIO端口可以与SRIO交换器件实现互联,也可以在C6455之间通过连接差分信号来实现。如图1和图2所示的1x模式和4x模式互联关系,在1x模式中,器件的任何一对发收信号可以与另一个器件的收发信号相互连接组成独立的1x模式工作。如果两个C6455间采用四对全连接方式,则可实现1个4x工作模式或者是4个独立的1x工作模式。

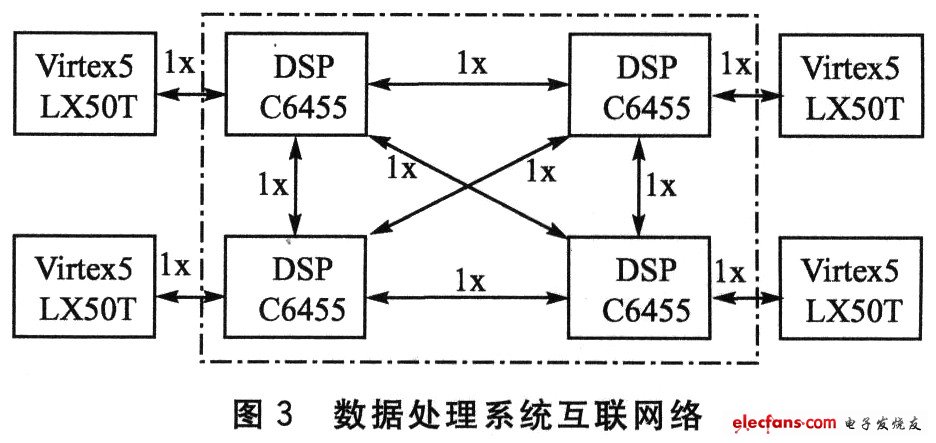

多DSP及FPGA的并行处理系统主要由4个C6455处理器和4个Virtex5LX50T构成,系统结构如图3所示。DSP与DSP之间的互联采用图1所示的连接方式来实现全连通的SRIO网络,实现所有DSP之间的1路1x通道,各个通道上的控制、传输独立并行工作。通过SRIO互联网络,任何一个DSP C6455都可以访问网络上其他DSPC6455资源,实现网络上的所有设备资源共享。而且这样的全连通结构又可以根据不同任务处理的特点,灵活地配置成菊花链串行流水线、一主多从的星形等拓扑结构,在不同数据处理应用中具有高度可动态重构性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)