如果您一直在关注有关半导体工艺技术的最新消息,那么您或许已经了解到全球最尖端代工厂将生产采用FinFET新型晶体管结构作为基本芯片构建块的器件了。这些待产的芯片将采用统称为16/14nm的工艺节点。不过您或许要问,FinFET到底是什么?与标准晶体管有什么不同?会带来什么样的优势和挑战?

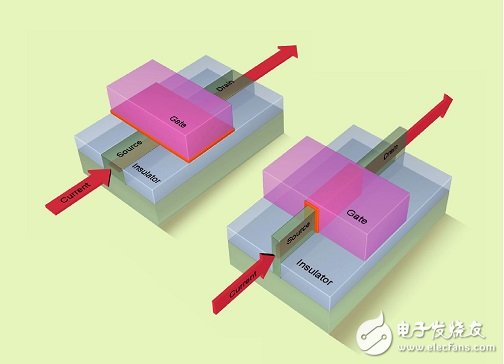

半导体制造技术的一项关键发明、当今2,920亿美元市值的半导体产业得以存在的一个关键因素就是Jean Hoerni于1950年代在飞兆半导体公司发明的平面工艺。平面工艺能实现更小型的晶体管,并将其安装在各种不同电路中,或者将它们高效连接在一起嵌入在平行面板上,而不必像印刷电路板上的分离式组件一样堆叠在一起。平面工艺实现了IC的极端小型化。随着平面工艺的实施,半导体可以分层内置或蚀刻在超纯晶圆片上。图1a显示的平面晶体管(其实是一个复杂的开关)包括3个主要特性:源极、栅极和漏极,它蚀刻并分层放置在芯片的基片上。图1b显示的是FinFET,请注意这里的栅极在三侧围绕信道,而平面晶体管上的栅极仅覆盖信道顶部。

源极是指电子进入晶体管的地方。根据栅电压,晶体管栅极在栅极下信道可以为开或关,类似于电灯开关的开启和关闭。如果栅极允许信号通过信道,那么漏极会移动电子到电路中的下一个晶体管。理想的晶体管在开启时能允许大量电流通过,而关闭时则应几乎不让任何电流通过,而且每秒会在开/关状态间切换数十亿次。切换速度是决定每个IC性能的基本参数。芯片设计公司将晶体管安排组织在各种电路中,再依次安排组织在功能模块(如处理器、存储器和逻辑块)中。这样,这些模块也能安排组织起来构成多种IC,实现多种神奇的电子设备功能,让我们受益匪浅。

自1960年代以来,半导体产业推出了一系列芯片创新技术,创新步伐与摩尔定律同步,也就是说每隔两年IC中的晶体管数量就会翻番。晶体管数量的翻番意味着今天的尖端IC包含数十亿个与二十世纪60年代芯片尺寸大小相同的晶体管,但运行速度呈指数级上升,功耗则呈指数级下降,电压为1.2V乃至更低。今天,晶体管非常微小,有些甚至只有几十个原子那么宽。

图1 –2D传统平面晶体管(a)和3DFinFET晶体管(b)的栅极位置不同

跟上摩尔定律的发展步伐面对半导体的进一步发展似乎受现实物理条件限制的情况,业界一直在努力跟上摩尔定律的发展步伐。过去10多年来,工艺技术专家努力确保平面晶体管的电子完整性。简而言之,平面晶体管的源极、栅极和漏极都非常小,性能要求又极高,因此这些晶体管已经不足以控制其中电子的流动。电子可能会外泄,或者即便器件关闭也可能从漏极流出。

对手机等电池供电设备而言,这就意味着电池耗电速度加快,即便手机关机也会快速耗电。对AC供电设备而言(即使用墙上插头供电的电器),这就意味着设备会浪费电力,而且更容易发热。如果热量过高,又不采取制冷散热措施,就会缩短产品的使用寿命,因为漏电会产生热量,而热量又会增加漏电。当然,制冷也会对设备造成额外的成本。泄漏问题对130nm工艺节点的半导体是最显而易见的。在这个泄漏问题极其严重的时代,微软不得不因为过热问题召回全球的Xbox 360。泄漏问题也是微处理器企业不得不采用效率较低的多核处理器、而不能使用速度更快但热量高得多的单处理器架构的原因之一。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)