近日合作媒体《天下杂志》一篇〈台积电真的超越英特尔?大客户这样吐槽……〉讨论台积电、三星的技术节点数字恐怕做过美化的问题引起不小的关注,这样的问题其实在先前即为半导体业界所持续论战,并在苹果 A9 芯片门事件,iPhone 6s A9 处理器分由台积电、三星代工时讨论来到最高峰,以实际情况而言,台积电、三星制程技术真的跟英特尔差很大?

半导体三雄纳米制程到底在争什么?

台积电、三星与英特尔的先进制程竞赛打得火热,在目前 14/16 纳米之后,制程战一路来到了 10 纳米。这些数字背后的意义其实指的是“线宽”,精确一点而言,就是金属氧化物半导体场效电晶体(MOSFET)的闸极长度(Gate Length)。

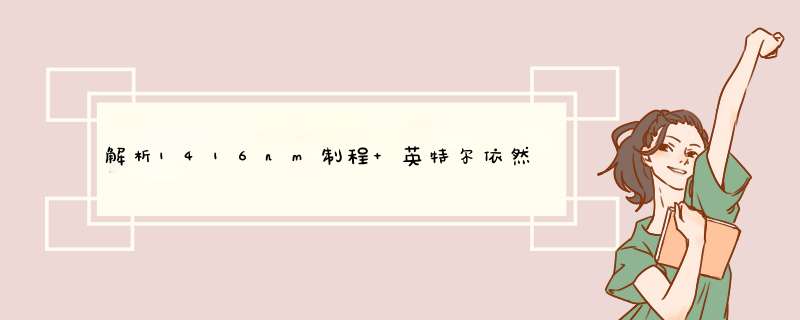

场效电晶体用闸极来控制电流的通过与否,以代表 0 或 1 的数码讯号,也是整个结构中最细微、复杂的关键,当闸极可以缩小,电晶体体积也能跟着缩小,一来切换速度得以提升,每个芯片能塞入更多电晶体或缩小芯片体积;再者,当闸极长度愈小,闸极下方电子通道愈窄,之间的转换效率提升、能量的耗损也能降低,收减少耗电量之效,但当闸极太薄,源极与汲极距离愈靠近,电子也可能不小心偷溜过去产生漏电流,加以也有推动力不足的问题,这也是为何制程微缩难度愈来愈高;台积、英特尔与三星群雄间争的你死我活的原因。

(Source:Hightech 科技台湾)

三者 14/16 制程节点数字都灌水?

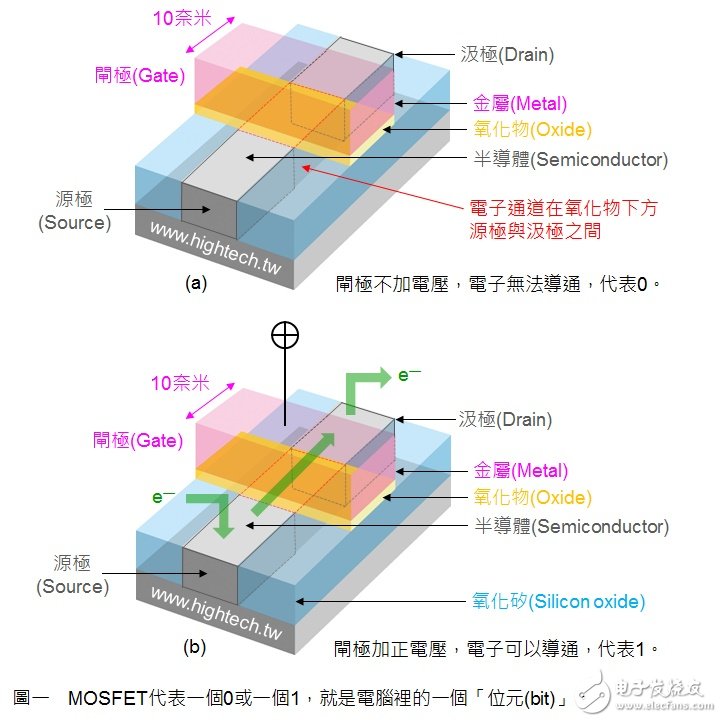

包含半导体芯片和系统还原工程与分析厂商 ChipWorks、Techinsights 与半导体分析厂商 Linley Group 都对台积电、三星、英特尔 16/14 纳米做过比较。

从 Linley Group 与 Techinsights 实际分析的结果,包含英特尔、台积电与三星在 14/16 纳米实际线宽其实都没达到其所称的制程数字,根据两者的数据,台积电 16 纳米制程实际测量最小线宽是 33 纳米,16 纳米 FinFET Plus 线宽则为 30 纳米,三星第一代 14 纳米是 30 纳米,14 纳米 FinFET 是 20 纳米,英特尔 14 纳米制程在两家机构测量结果分别为 20 纳米跟 24 纳米。

(Source:Linley Group)

(Source:Techinsights)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)