1 带隙基准电路的基本原理

带隙基准电压源的目的是产生一个对温度变化保持恒定的量,由于双极型晶体管的基极电压VBE,其温度系数在室温(300 K)时大约为-2.2 mV/K,而2个具有不同电流密度的双极型晶体管的基极-发射极电压差VT,在室温时的温度系数为+0.086 mV/K,由于VT与VBE的电压温度系数相反,将其乘以合适的系数后,再与前者进行加权,从而在一定范围内抵消VBE的温度漂移特性,得到近似零温度漂移的输出电压VREF,这是带隙电压源的基本设计思想。

1.1 带隙基准电压源核心电路

本文提出的电路核心结构如图1所示,在电路中双极晶体管构成了电路的核心,实现了VBE与VT的线性叠加,获得近似为零温度系数的输出电压。图1中双极型晶体管Q1和Q2的发射区面积相同,Q3和Q4的发射区面积相同,考虑设计需求,取Q1和Q2的发射区面积为Q3和Q4的发射区面积的8倍。

假设双极晶体管基极电流为零,运放的增益足够大,则a点和b点的电压相等,即:

在实际电路中,经过计算可知当取R3/R1=2.3066时,可以得到室温下的近似零温度系数的输出参考电压。

1.2 带隙基准电压源总体电路

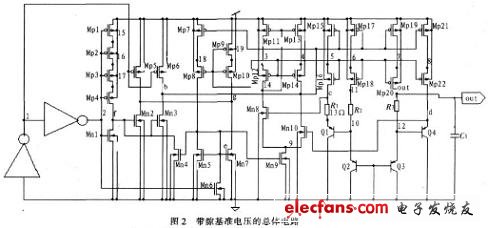

带隙基准电压源总体电路总共由4部分组成:A部分是启动电路,B部分提供偏置电压,C部分是运算放大器,D部分是带隙电压源的核心部分。其中核心部分是由双极晶体管构成,实现了VBE和VT的线性叠加,获得近似零温度系数的输出电压。总体电路如图2所示。

1.3 运放的失调对基准源的影响

基准源中运放的设计是非常重要的,运放的失调是基准源的一个主要误差源。由于不对称性,运放会受到输入失调的影响。假设失调电压为Vos,经计算得到含失调电压的输出公式为:

可见,Vos的大小可能导致相当大的基准源输出电压误差。此外,Vos自身是温度的函数,和理想运算放大器相比,会引入一定的误差,而由运算放大器电源抑制比PSRR引入的误差可以折合成失调输入电压Vos也将和电源有关。这样,为了减小失调对基准电压的影响,运放的失调就要尽可能地小。然而,引起失调的原因有许多,如晶体管之间的不匹配、运放输入级管子阈值电压的不匹配、运放的有限增益等等。因此,实际上,Vos是很难完全消除的,但通过提高运放的增益和细致地设计版图可以减小它对基准电压的影响,提高基准电压源的精度。

1.4 电源抑制比

电源抑制比(PSRR)是电路对电源电压频率变化的抑制能力,是从运放的输入到输出的开环增益与从电源到运放输出的增益之比,用KPSR表示。对带隙基准而言,由于输出电压和Vdd无关,所以Vdd的变化基本上不会影响输出参考电压的影响。但是随着工作频率的提高,由于电容耦合的原因导致输出电压在高频时会受到Vdd的波动的影响,从而影响输出电压的稳定性。具体的电路设计中考虑了这一点,在电路中采用了自偏压cascode结构的电流镜,同时在输出端接一对地滤波电容,输出电压的电源抑制特性就得到了很好的提高。

1.5 启动电路

启动电路也是带隙基准源中一个重要的部分。如图2中A部分所示,电路可能会出现零输出的情况。因为放大器两端的输入都为零电平时,电路处于一种不工作状态,因此需要一个启动电路来打破这种平衡。图中引入的启动电路由Mp1~Mp6和Mn1~Mn4组成。其工作原理是由Mp1~Mp4,Mn1组成的反向器驱动Mn2和Mn3,使Mn2和Mn3导通,从而通过a点和b点间接给运算放大器的两个差分输入端提供偏置电压,保证在系统加电的时候,输入差分对不会关断,当电路正常工作后,启动电路关断。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)