通常情况下,设计隔离式DC-DC转换器时遇到的最大阻碍便是变压器设计,设计者往往因此望而却步,从而选择其它更简捷的设计任务。利用市售的栅极驱动变压器特性,就可以获得四个单独的隔离直流输出。实际上,对于小功率DC-DC电源转换,栅极驱动变压器是个理想的选择,因为这种变压器已经做了电压和时间大乘积(ET或伏特微秒乘积)以及低漏电感的优化。

一款高磁导率且在高开关频率(FSWX)下有低损耗的磁芯可支持一般的10V~15V初级电压,且在100kHz~500kHz开关频率时有500ns~5μs的典型导通时间。该电压和时间范围正是DC-DC转换器设计所需。同时,已经针对低泄漏电感选择了一种磁芯几何尺寸以及绕组结构,以减少上升和下降时间,同时有低的振铃。最后,所使用的线规足以让DC-DC 转换器处理数10mA级的绕组电流,而没有过多的铜线损耗。

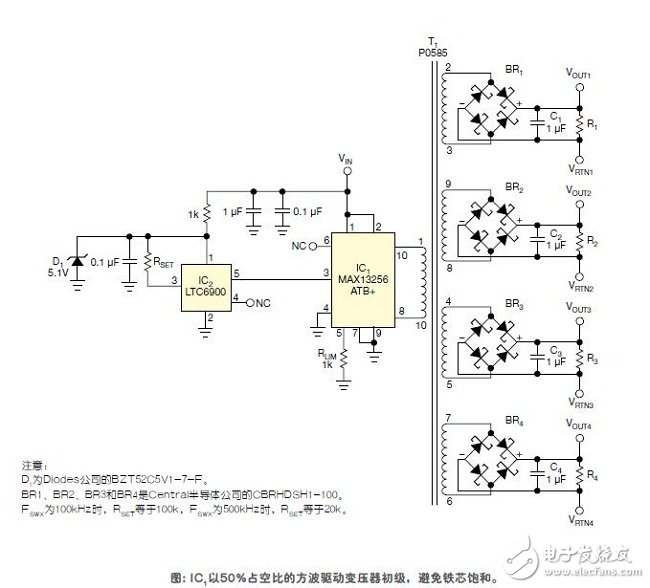

Pulse Electronics公司的P0585栅极驱动变压器含有五个绕组,每个绕组圈数都相同(参考文献1)。其中一个绕组使用三层绝缘线(TIW),另外四个绕组使用标准绕组线。TIW绕组作为初级驱动,可获得一个RMS为3kV的标称主次级击穿电压。四个次级绕组之间的额定击穿电压并未确定,不过这种导线绝缘方式通常会用于离线电源情况,此时,各绕组之间的电压可高达400V。

隔离式电源输出提供了很大的灵活性。使用这种方式可以在不同地电势情况下,更加方便地打断接地环路,为远程电路供电,并且简化了对正负输出电压极性的选择。下图展示了这种变压器的四个次级绕组,它们产生四个独立的等电压输出。但这四个次级绕组可以有多种串/并结合,从而产生大量输出电压/电流的组合。

美信半导体生产的MAX13256H-桥电路变压器驱动器(IC1)最适合用于此类应用。它包含一个独立的变压器隔离DC-DC转换器所需要的全部功能。其内置FET可承受36V电压,并配置为两个独立的推挽式输出,以精确的50%占空比驱动变压器的初级,避免了铁芯饱和。该驱动器还包含可调的、强健的内部限流功能,从而为输出提供短路保护,且在故障排除之后能够完美地恢复。该驱动也包含欠压锁定(UVLO)功能,在输入电压过低时阻止开关活动。

增加的凌力尔特公司LTC6900时钟源(IC2)用于精确地调整开关频率。MAX13256本身有一个内部时钟,但是考虑到整个系统的兼容性或 EMI原因,大多数用户可能会更倾向于自己设定开关频率。MAX13256支持使用一个外部TTL电平时钟,而且其UVLO特性确保IC1的VIN极上升到导通阈值前,IC2就上电并运行。RSET的值决定了IC2的输出频率,该频率设定为所需IC1开关频率的两倍。

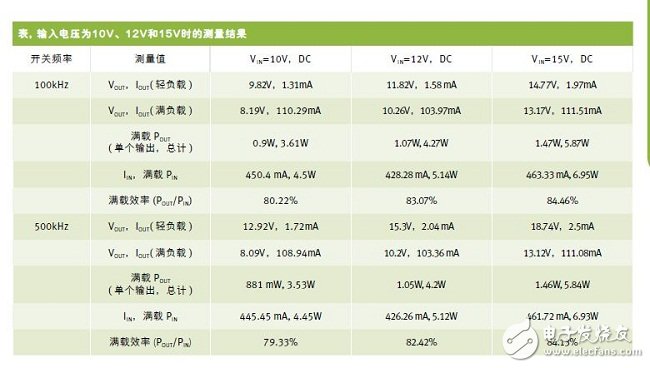

上表中为开关频率为100kHz和500kHz时,输入电压为10V、12V和15V情况下的测量结果。由于采用高开关频率、低漏电电感及肖特基桥式整流器,即使用了低值(1μF)的表面安装陶瓷输出电容,输出电压的纹波也很小,不到20mV峰峰值。表中还给出了效率,以及因输出未稳压而造成输出电压与负载电流之间的变动关系。如果需要更低的噪声或者严格稳定的直流输出,可以使用线性稳压器来调节输出电压。

从这些测量结果可看出,满载是产生500mA峰值初电流时的负载。这是当RLIM为1kΩ时的MAX13256最小限流阈值。一些设计者可能想在低于这些经验性的满载电流水平上进行 *** 作,从而获得更多裕度,以防止虚假的大电流触发。在较高开关频率下可以看到轻载输出电压的提升,原因是:这是一种为求简捷和高效而使用了较少阻尼器的设计。随着开关频率升高,产生了更多的漏电感能量,这些能量传递到次级绕组,提高了所测得的输出电压。

以下为检验该变压器运行参数是否符合数据手册规范的简要说明。P0585变压器有一个95Vμsec最大ET乘积。这个计算结果是初级绕组上施加的最大电压与该电压所持续最大时间(导通时间)的乘积。由于MAX13256是以精确的50%占空比驱动变压器初级,最大ET乘积将出现在输入电压为15V 时。在本设计中的100kHz最小开关频率下,最长导通时间为5μs,所以最大ET乘积为75Vμsec,该值符合数据手册规范。

峰值磁通密度规格为2100G。在计算峰值磁通,数据手册中的方程式2A和2B均基于VIN和开关频率。同样,峰值磁通密度出现于VIN为15V且开关频率为100kHz时。注意在方程式2A中,“DON”为50%占空比或0.5,而不是单位为微秒的时间。在这些情况下,所计算的峰值磁通密度为 1512高斯,符合数据手册中的规格。

运用变压器数据手册中的公式可计算出磁芯损耗。在100kHz时,损耗为0.468W,在500kHz时,损耗为0.117W,后者数值较小,原因是有较低的ET积。

运用变压器数据手册中的公式可算出铜线损耗为93.75mW。这个计算铜线损耗的简化公式是基于绕组的I2R损耗,而未考虑绕组的趋肤或接近效应。因此,这些简化结果与频率无关,而是基于初级绕组中的±500mA峰值电流,以及四个次级绕组中各自的±125mA峰值电流。

使用变压器数据手册中的升温公式以及上述计算的总损耗(100kHz下为561.75mW),可得预期变压器的温升为37.2℃。

本设计使用P0585栅极驱动变压器,您也可以使用其他(更小的)市售栅极驱动变压器,尤其是需要较少电压输出,以及较小电流的时候。只需要确保您参照本设计所述方法检查了变压器的最大Vμsec规范。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)