在移动计算时代,片上系统(SoC)的设计已经变得更为复杂,因为在设计过程中面临着诸多挑战,如需遵循针对高级流程节点的复杂设计规则,需采用低功率电路设计技术,并放大电路的尺寸。电源完整性是设计方案能被成功签核的关键因素之一。本文介绍了一种新的工具,与其他现有技术相比较,它不仅能将电源完整性分析与签核的速度提高10倍,同时还能达到类似于集成电路通用模拟程序(SPICE)的准确度。该工具将一套完整的设计实现和签核工具整合到一起,以便更好地克服在签核过程中遇到的挑战,从而实现业内最快的设计收敛流程。

简介

为了满足移动计算的各种要求,片上系统的设计变得越来越复杂。随着消费者开始青睐更小巧、性能更好、电池续航时间更长的设备,设备中所使用的芯片必须能提供更丰富的功能,更低的能耗以及更小的尺寸。对设计工程师来说,这些变化意味着他们在设计过程中必须运用先进的电源技术(例如电源控制开关)、增加知识产权的内容和功能(例如模拟/混合信号宏指令)以及减少设计裕度(例如电源电压小于1V)。另一方面,产品上市周期变得越来越短,因此在设计周期的最后阶段,电源签核对成功将设计方案送交制造来说至关重要。

至今,可用的电源签核技术仍未能跟上创新的步伐。例如,一直以来额外的运行时间都是妨碍设计者们完整而全面地进行电源完整性分析和优化的一个瓶颈。然而,现在有一种新工具可以解决这个问题,它利用先进的大规模并行算法和分层结构将电源完整性分析和签核的速度提高到原来的10倍,同时还能达到类似于SPICE 的准确度。另外,作为从芯片到系统的整套流程中的一部分,该工具通过提高整个设计周期的生产力而加速设计收敛流程。

日益复杂的产品设计亟需电源完整性分析新工具

产品设计的复杂度越来越高,产品尺寸越来越小,而且对产品分析的要求也越来越复杂,这增加了完成电源完整性分析和签核所需的时间。如果使用“平面”设计方法把设计拉平成为高级别的一层,则不足以分析拥有数亿实例的超大规模设计。当前的解决方案趋向于将设计分析划分成与“单点工具”对应的多个部分,这些工具在准确性或易用性方面并不能达到高级片上系统的要求。

另外,由于当前的解决方案是使用单点工具,因此无法有效地评估电源对时序收敛的影响,而时序对电源(VDD)却是最为敏感的。此外,高级节点设计技术及技巧(如FinFET工艺和三维芯片(3D-IC)封装)也带来了新的挑战。例如,随着FinFET器件的部署,会因为垂直电流方向、功率密度增加等因素而产生新的电迁移规则。而随着三维堆叠式芯片的部署,会有电热协同仿真的新需求。为了让设计工程师们满足上市周期和产品质量的相关要求,需要一个涵盖芯片、封装以及系统的完整电源完整性分析方案。

完美的电源完整性分析工具需具备哪些功能?

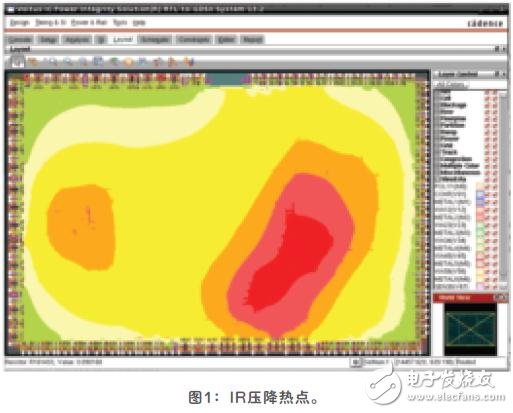

当出现漏泄增加、温度变化,或者由于静态和动态IR压降造成工作电压下降等场景时,一项设计可能失败。无论是对于数百万门级设计还是对于多颗裸晶而言,能在设计早期阶段就对电源和IR压降约束进行调试并证实其符合要求,是节约宝贵的开发成本和时间的关键。换句话说,尽早找到芯片上的“热点”有助于防止芯片性能下降(图1)。

为了能更好地支持高级片上系统设计,完美的电源完整性分析工具应具备以下功能:

● 能计算芯片上的漏泄以及开关和内部耗能;

● 能对电源网络的电源完整性进行分析(IR压降检测及电迁移检测);

● 能就电路中去耦电容单元和电源控制开关的最佳尺寸和布置方式提供建议,从而对设计方案中的物理实现电流进行优化;

● 能评估IR压降对包括静态时序分析在内的设计收敛的影响。

利用在生产过程中已得到验证的和具备签核质量的算法和引擎,Cadence公司开发出了一种既能覆盖整个芯片又能顾及芯片上所有单元的新型电源完整性分析工具(即Voltus集成电路电源完整性分析解决方案),该工具能提供上述所有功能。它的分析速度比其他同类解决方案快10倍,同时还提供了类似于 SPICE的准确度。此外,台湾积体电路制造股份有限公司(TSMC)已经通过16nm级FinFET工艺对这种工具的性能进行了验证。因此,工程师们可以相信该工具能够跨越不同的设计规则而给出准确的分析结果。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)