系统级节电与功率预算优化是许多应用的关键。例如,数据中心运营商努力控制能耗,便携式设备设计人员力图降低流耗实现更长的电池使用寿命,而通信系统则需要降低工作温度提高稳定性。电源设计主要规范的当前着眼点是:1)在整个负载电流范围内最大限度提高效率;和 2) 根据负载需要自适应缩放输出电压。

DSP、FPGA 以及 ASIC 现在具有类似的功能,可根据器件活动、电源及时钟域配置、工作模式以及工作温度,实现最大限度的功耗降低。虽然支持 VID[1] 的数字化脉宽调制器 (PWM) 控制器解决方案可用来满足这一需求,但确实也需要对无处不在地模拟控制负载点 (POL) 稳压器进行输出电压数字化调节。在调节过程中,可轻松调整模拟电源实施(或许已经完成设计或已经通过测试台测试),满足其它方案无法实现的系统级功率预算与成本目标要求。

数字输出电压调节

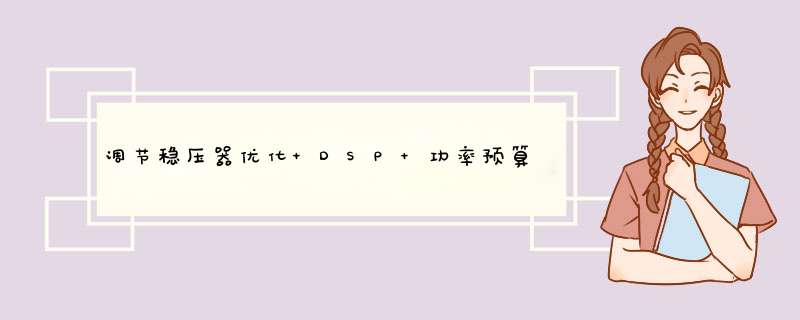

鉴于上述设计目标中的优势利益,TI 现在提供一款 VID 编程器[2]作为专用标准产品 (ATSP)。图1 是用于补充模拟型 POL DC/DC 解决方案的 LM10011,其包含高精度数字可编程电流数模转换器 (IDAC),支持模式可选 4 位及 6 位 VID 接口。IDAC_OUT 引脚的精确 DC 电流与 4 位或 6 位数字输入字成比例,可输入到输出稳压环路的反馈 (FB) 节点。随着输入字的累加,IDAC_OUT 电流可降低,从而可根据稳压器反馈电阻器调高输出电压设置点。FB 节点一般由模拟控制环路的误差放大器保持在恒定电压下。

图1:常规POL 稳压器与电流 DAC 配对,构成6 位数字VID 接口

该实施过程中最为重要的是 VID 解决方案与模拟 POL 稳压器设计方案的兼容性。POL 可有效部署为 DSP 的从设备。根据设计,该 IDAC 解决方案可帮助 DSP 及其它数字负载实现其全面的节电性能,降低功耗,例如在通信基础设施应用中。实际上,该款 VID 解决方案主要用于与任何 POL 稳压器一起工作,调节 KeyStone™ 多核 DSP [3] 等支持 VID 功能的处理器的内核电压 (VCORE)。

DSP 内核电源

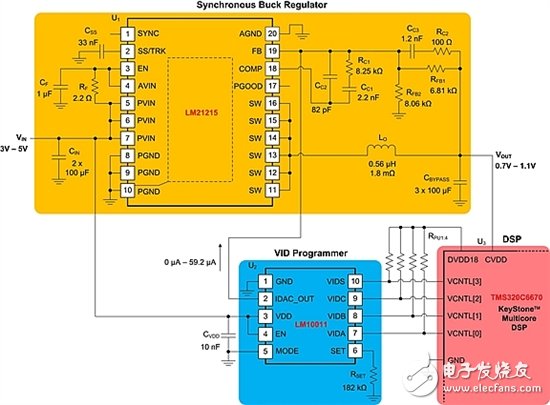

图 2 是同步降压 POL 稳压器提供的、具有内核电压 CVDD 的多核 DSP 原理图。电源级包括 15A 电压模式稳压器、560nH 电感器以及陶瓷输入输出滤波器电容器[2]。来自 DSP 的 6 位 VID 命令有助于根据 DSP 性能要求的不断变化调节输出电压 VOUT。

图2:使用可调节性受VID 控制的同步降压稳压器为支持内核电压轨的多核DSP/SoC 平台供电

根据图2 所示的系统实施方案,具体控制方案针对 6 位 VID 使用了 4 线 (VCNTL) 接口,从而可在 VID 工作中实现更高的分辨率或精细粒度。IDAC_OUT 电流具有 59.2µA 的最大满量程范围 (VID[5:0] = 000000b = code 0)。在 6 位模式下,这可提供分辨率为 940nA 的 64 种设置以及优于 1% 的误差精度。

输出电压由 DSP 判定为电压介于 0.7V 至 1.103V 之间的电平。这相当于 VOUT 调节分辨率为 403mV/63 或 6.4mV。压摆限制可防止输出发生突变。而 VID 的抗尖峰脉冲滤波器则可提供噪声抗扰度(实际上是在 VID 线路的转换与 IDAC_OUT 电流的后续变化之间添加一个小小的延迟)。在接收到 VID 命令之前的启动过程中,IDAC_OUT 电流可根据 RSET 值,假设为 16 个分立电平之一。这允许 DSP 的内核电压在各种电平下上电,实现更高的系统灵活性与可靠性。

但值得注意的是具体的 DSP 可能无法支持所有的电压或范围。例如对 KeyStone I DSP 而言,预期工作范围在代码 31 和 50 之间(0.905V 至 1.020V)[4]。图2 中 LM10011 的电源电压来自输入总线。另一种选项是使用 PWM 控制器提供的、或系统中其它地方(如果有)提供的额定 3.3V 或 5V 偏置电压轨。无需在 DSP 和电流 DAC 之间使用电平转换器或胶合逻辑。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)