Verilog始于20世纪80年代初,是一家名为Gateway Design AutomaTIon的公司的专有硬件描述语言(HDL)。最初的Verilog HDL的主要作者是Phil Moorby。

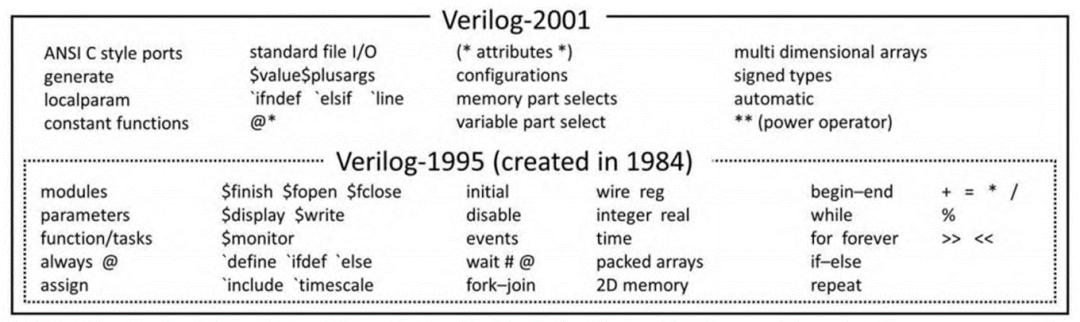

IEEE于1993年接管了Verilog语言,并在两年后发布了正式的IEEE Verilog HDL标准,即IEEE 1364-1995,昵称为“Verilog-95”。五年后,IEEE发布了1364-2001,绰号为“Verilog2001”,其中有许多用于建模和验证数字设计的增强功能。

下图显示了Verilog-95中的主要语言功能,以及Verilog-2001中添加的主要新功能。请注意,此图并不是语言特性的全面列表。其目的是展示Verilog-2001添加到原始Verilog语言中的主要新功能。

从Verilog发布到今天,其已经经历了四十年的风雨,早期的“电路”设计Verilog的确很方便,尤其在那个年代,其也崔进了集成电路的发展。但是“老”不代表方便,尤其高速发展的今天,集成电路以摩尔定律指数发展,FPGA的应用场合以越来越复杂,复杂的逻辑设计让这个“老人”有些力不从心,今天我们就简单总结一下Verilog在设计时候的不方便地方。

Verilog的“贪婪”下面是一个很常见的错误:

Unable to bind wire/reg/memory `D' in `tb_alu_8bits.U0.$ivl_for_loop0' 1 err

变量D未声明

声明的“贪婪”需要这么多声明吗?

大家在进行逻辑设计时候是否对于变量申明感觉很烦,对于无休无止的变量声明和位宽声明,很容易在设计时候引进错误。

尤其对于一些综合器在推断变量的类型及位宽时候的错误很难检查出来,只有在进行仿真及验证的时候才能发现问题。

Verilog的“傲慢”Verilog 是一种弱类型和有限类型的语言,就导致其错误检测很弱。

PS:VHDL是强类型语言,SystemVerilog在兼容Verilog部分是弱类型,其他部分基本都是强类型。强类型的好处是在验证过程中尽早发现设计中的错误。

一些错误在进行设计时候,Verilog并不会爆出错误,但是会导致功能有问题,这种问题很难检查出来,比如位宽不匹配、跨时钟域、锁存器等问题,这是因为Verilog会自动进行位宽匹配,只有在进行linTIng时候会爆出来警告,综合时候基本不会爆出错误。

错误检测的“傲慢”傲慢到不让我进行检测!

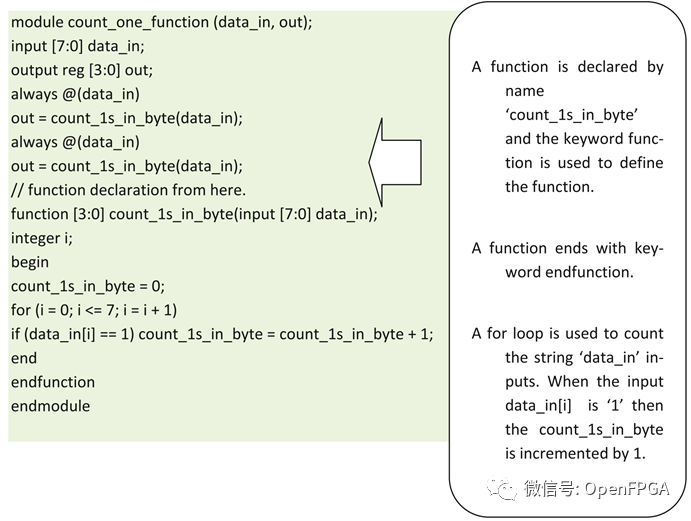

Verilog的“色欲”不知道大家设计时函数或者任务用的多不多?

我猜肯定不多,而且很多Verilog入门教材中都是不建议使用函数或者任务,主要是因为Verilog使用函数或者任务有很多限制。

函数的限制:

-

函数不能由时间控制语句甚至延迟运算符组成。

-

函数至少有一个输入参数声明。

-

函数可以由函数调用组成,但函数不能由任务组成。

-

函数在零模拟时间内执行,并在调用时返回单个值。

-

在编写可综合 RTL时,不建议使用函数。

-

函数用于编写行为或可仿真模型。

-

函数不应具有非阻塞赋值。

任务的限制:

-

任务可以由时间控制语句甚至延迟 *** 作符组成。

-

任务可以有输入和输出声明。

-

任务可以由函数调用组成,但函数不能由任务组成。

-

任务可以有输出参数,在调用时不用于返回值。

-

任务可用于调用其他任务。

-

在编写可综合RTL时,不建议使用任务。

-

任务用于编写行为或可仿真模型。

以上的种种限制,你确定你设计的函数或者任务能简化你的设计吗?

函数、任务的“色欲”爱我却不让我广泛使用你~

上例是从给定字符串中计算1个数的设计。在本例中,函数与参数“data_in”一起使用。函数名为“count_1s_in_byte”。在大多数协议描述中,需要对输入字符串执行一些 *** 作。在此示例中,字符串为8位输入“data_in”,输出结果为4位“out”。不建议使用该函数进行综合。

Verilog的“懒惰”当你设计了一个功能module,下一个文件想引用时候就需要例化,当你的设计比较复杂时候(有几十个module)你就会发现Verilog的例化极其不方便,需要手动例化,不仅浪费时间而且很容易出错(对于初学者这种错误很常见)。

例化的“懒惰”例化能不能不这么懒!

Verilog的“嫉妒”Verilog不像VHDL有丰富的包文件,同时也没有像一些高级语言库文件(不奢求)。同时自己的参数化也不是很方便(宏做参数化时候,几十个变量情况怎么办?)。

现在我需要做一个乘法器,我需要花费很长时间去了解乘法器的结构,然后去设计和优化,如果有一个math包那是不是会大大减少设计时间呢?

库、包的“嫉妒”Verilog很嫉妒别的语言丰富的库、包文件(Python:你直接念我身份z)。

Verilog的“暴食”对于复杂设计,Verilog设计基本都是以“年、月”进行计时的,对于时间简直就是恶魔。

调试的时候更是麻烦,增减一个信号或者改动一个小小逻辑都需要重新综合(调整时序时候需要插入寄存器的时候,想想都恐怖~)。

时间的“暴食”大型设计以月为时间进行计时,调试时候更是“摸鱼”党的福利~

Verilog的“暴怒”由于上面的各种缺陷,导致一些老工程师在编写Verilog时候为了保证综合性及正确性会将设计的“逻辑性”很强,如果没有好的注释,就会导致其他人在读代码时候可读性比较差(SV在这方面改进了很多,使代码的自读性加强)。

注释的“暴怒”没有注释看得你“抓狂”。

总结上面的观点比较偏激,都是拿着Verilog的缺点对比其他语言的优点,大家看看笑笑就好了,千万别较真,任何语言都有自己局限性,如果有那么优秀的编程语言,目前就不会出现几十上百种设计语言了。

Verilog有自己的缺点,但是也在逐步完善~

参考

https://zhuanlan.zhihu.com/p/89249985

https://www.campera-es.com/vhdl-vs-verilog-vs-systemverilog

https://www.quora.com/What-are-the-advantages-and-disadvantages-of-System-Verilog-compared-to-Verilog-or-VHDL

图片来源:

https://en.wikipedia.org/wiki/Seven_deadly_sins

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)