如今的智能产品越来越多地需要将传统的实时嵌入式设计需求与要求更高的应用级软件结合在一起。除了更大的计算负载外,这些产品还需要支持通过先进的媒体服务(如触摸屏、高分辨率 3D 图形和图像传感器)与用户交互。

随着需求的扩大,开发人员在减小功耗、成本和系统尺寸方面所面临的压力也更大,因此不得不寻找更有效的方法来替代传统的多子系统设计。

本文将讨论这些设计需求的演变,以及到目前为止,处理器是如何满足这些需求的。然后将介绍并展示如何使用 NXP Semiconductors 的新型处理器。这些处理器为开发人员提供了一种更简单的满足这一不断增长的需求的解决方案,让设计能够同时处理实时计算和应用计算要求。

升级处理器并保持代码投资

开发人员通常使用与特定应用处理要求匹配的多核微处理器来升级其设计的计算能力。使用这种方法,开发人员既可实现性能提升,又可保持与现有代码库的兼容性,以及相应器件系列的使用体验。

例如,使用 NXP i.MX 6 应用处理器系列,设计人员不仅可以保持代码兼容性,而且能够使用配备单个 Arm® Cortex®-A9 应用处理器内核的 i.MX 6Solo、配备两个内核的 i.MX 6Dual 或集成四个内核的 i.MX 6Quad,来提升性能。

这种升级应用处理能力的需求,也在曾被视为传统嵌入式系统的设计中快速发展。对于这些设计,产品制造商希望为家用电器、工业控制器、医疗仪器等设备增加智能性。为此,半导体供应商提供了异构多核处理 (HMP) 器件,这些器件可同时集成应用处理器内核和嵌入式处理器内核。例如,NXP i.MX 8M 系列结合了多至四个 Arm Cortex-A53 应用处理器内核,以及一个 Arm Cortex-M4 嵌入式处理器内核。

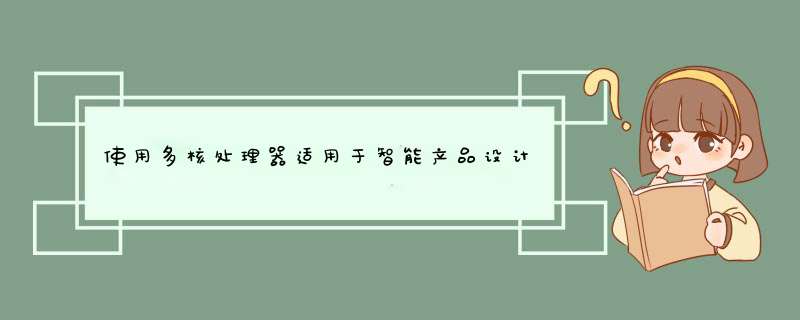

只需使用这一单个器件,开发人员就可以打造出智能音频产品。这些产品可充分利用应用处理器来增强、过滤或以其他方式处理音频数据。然后,音频系统依靠嵌入式处理器内核来执行播放所需的实时功能(图 1)。在嵌入式处理器执行实时 *** 作期间,应用处理器可以置于低功耗模式,从而降低整体功耗。当实时 *** 作完成时,嵌入式处理器只需向应用处理器发送唤醒信号。

图 1:异构多核处理器尤其适用于智能产品设计,既可提供高性能计算与实时功能,同时又不影响紧张的功率预算。(图片来源:NXP Semiconductors)

除了异构内核外,NXP i.MX 8M 系列还集成了各种多媒体资源,包括 4K 视频处理单元 (VPU) 和高性能 3D 图形处理单元 (GPU)。因此,该系列可以为越来越多的视频及 3D 图形智能产品提供有效解决方案。

尽管如此,开发人员在构建高性能系统时,仍然面临着电池及线路供电系统对低功耗需求日益增长的挑战。为应对这一挑战,NXP i.MX 8M Mini 处理器系列采用先进的半导体工艺技术制造,可解决高性能混合负载处理与功耗降低之间的需求矛盾。

高性能、低功耗计算

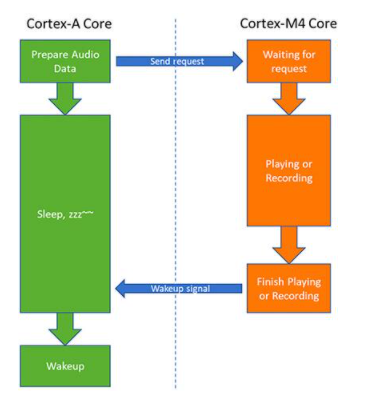

NXP i.MX 8M Mini 处理器属于首款采用 14 纳米 (nm) FinFET 工艺技术制造的 NXP HMP 系列,专为新兴的工业和物联网 (IoT) 系统而设计,这些系统对高性能、高安全性和低功耗都提出了要求。与 NXP i.MX 8M 系列一样,NXP i.MX 8M Mini 也集成了一个 Arm Cortex-M4 嵌入式处理内核,以及最多四个 Arm Cortex-A53 应用处理内核,还有一个全面的安全子系统以及多个连接和 I/O 选项(图 2)。

图 2:NXP i.MX 8M Mini 处理器结合了最多四个 Arm Cortex-A53 应用处理器内核和一个 Arm Cortex-M4 嵌入式内核,还有新兴智能产品所需的全套安全、多媒体、系统功能以及 I/O 接口。(图片来源:NXP Semiconductors)

为了支持嵌入式设计,与之前的 NXP i.MX 8M 相比,i.MX 8M Mini 减少了某些 I/O 通道的数量及其多媒体子系统的高分辨率能力。例如,i.MX 8M Mini 器件包括商业版 (MIMX8MM6DVTLZAA) 和工业版 (MIMX8MM6CVTKZAAA),提供一个单一着色器 GPU 和一个 1080p 60 赫兹 (Hz) VPU,而 NXP i.MX 8M 则提供四着色器 GPU 和 4K VPU。i.MX 8M Mini 系列的其他成员包括商业版 (MIMX8MM5DVTLZAA) 和工业版 (MIMX8MM5CVTKZAA) 器件,则完全去除了 VPU。与早期的 NXP i.MX 8M 一样,i.MX 8M Mini 能够让开发人员利用处理器对多种存储器类型的支持(包括双倍数据速率 3 低电压 (DDR3L)、DDR4 和低功耗 DDR4 (LPDDR4)),实现性能与成本之间的进一步平衡。

降低功耗

为了进一步优化性能和功耗,开发人员可利用 NXP i.MX 8M Mini 功能,以自动或编程方式切换到低功耗工作模式。在一定条件下,应用内核可以自动切换到空闲模式,并且关闭 GPU、VPU 和应用内核,同时对大多数内部逻辑进行时钟选通,但保留对 L2 数据缓存的供电。在此模式下,Arm Cortex-M4 内核仍可继续运行,以执行更多传统嵌入式处理任务,如传感器数据采集等。

挂起模式是最省电的模式,通过同时禁用用于管理存储器接口的双倍数据速率控制器 (DDRC),延长空闲状态下功耗降低的时间。最后,安全非易失性存储 (SNVS) 模式只保留对 SNVS 逻辑和实时时钟的供电。

i.MX 8M 中采用的 14 nm FinFET 工艺技术具有功耗降低特性,在挂起和 SNVS 模式下表现尤为明显。在采用 FinFET 的 i.MX 8M Mini 中,挂起模式的功耗大约为 7.81 毫瓦 (mW)。而在早期的 i.MX 8M 中,功能类似的模式(称为深度休眠模式)消耗 197 mW。类似的功耗降低也发生在 SNVS 模式,在该模式下,i.MX 8M Mini 的功耗约为 0.11 mW,而早期的 i.MX 8M 功耗约为 17 mW。

像 i.MX 8M Mini 这样的复杂器件具有大量的功能块和微调工作模式,使工程师面临诸多严格的实现要求。与其他同类器件一样,i.MX 8M Mini 也依赖多个功率域来优化电源管理和效率。要启动和关闭这些器件,必须严格遵照指定的上电和断电顺序。

对 i.MX 8M Mini 上电时,首先为 SNVS 存储体中的 GPIO 前级驱动器加电,通常为 1.8 伏。在 2 毫秒 (ms)(最多 2.4 ms)内,必须为 SNVS 内核逻辑加电,通常为 0.8 伏。随后,再通过 12 个步骤,按顺序将特定信号或电力供给 i.MX 8M Mini 的各个引脚,每一步按 0.015 ms 到 20 ms 间隔定时进行。

为器件断电的顺序正好相反,但是连续步骤之间的延迟均为 10 ms。无论是哪一种情况,若不遵守这些准则,都可能使器件无法启动,导致上电期间电流过大,或者在最坏的情况下,会造成器件发生不可逆转的损坏。

处理器的 PC 板物理设计也有自身的严格要求。对于处理器 486 焊球 14 x 14 毫米 (mm) 封装的布局,NXP 建议使用至少 8 层的 PC 板层叠结构,并分配足够的层专门用于电源轨,以满足电流电阻 (IR) 下降规范的要求。与此同时,布局工程师必须确保高速线路上的串扰最小,包括受支持、以 1.5 千兆赫 (GHz) 和 3,000 百万次/秒 (MT/s) 速度运行的存储器器件线路。

快速开发

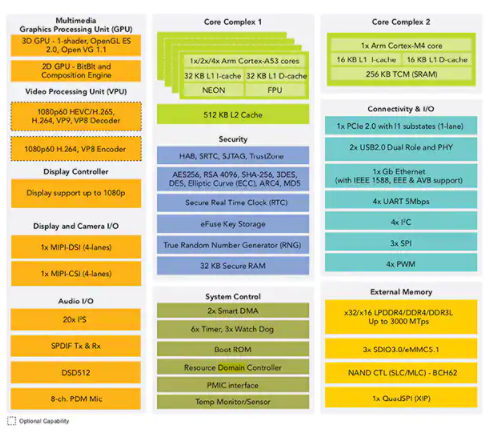

为帮助工程师快速开始应用开发或加快定制硬件设计的开发,NXP 推出了 NXP i.MX 8M Mini EVK(评估套件)和相关的参考设计(图 3)。该评估套件以基板和系统级模块 (SOM) 板形式交付,提供了一个完整的系统,包括外部 LPDDR4 存储器和闪存,以及 USB 和其他接口。

图 3:NXP i.MX 8M Mini EVK 板组提供了一个完整的系统平台,用于立即评估 i.MX 8M Mini 处理器,以及快速开发异构多核处理器应用。(图片来源:NXP Semiconductors)

除千兆位以太网外,该套件还包含 Wi-Fi 和蓝牙连接选项。提供的扩展板包括 MINISASTOCSI 相机模块和 MX8-DSI-OLED1 有机发光二极管 (OLED) 触摸屏,用于帮助进行视频和显示应用设计。

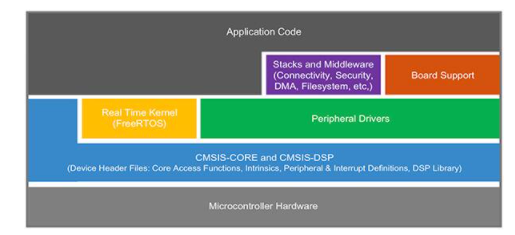

借助用于嵌入式 Linux® 和嵌入式 Android® *** 作环境的可用预建镜像,开发人员可以立即使用该套件评估 i.MX 8M Mini 处理器,并运行样例应用程序。对于构建自己的软件应用的开发人员,NXP 免费提供 MCUXpresso 软件开发工具包 (SDK),该工具包提供了一整套软件组件,用于构建典型的高性能嵌入式应用(图 4)。

图 4:MCUXpresso 软件开发工具包 (SDK) 架构由整套软件层组成,包括驱动程序、板级支持包,以及开发大多数嵌入式应用所需的可选组件。(图片来源:NXP Semiconductors)

使用 NXP 的在线 MCUXpresso SDK Dashboard,开发人员可以针对 GCC Arm Embedded 工具链或用于 Arm 的 IAR Embedded Workbench 进行 SDK 配置,还可以添加可选的中间件组件,包括 Arm Cortex 微控制器软件接口标准 (CMSIS) DSP 库和 Amazon FreeRTOS。配置后的 SDK 分发包将包含 Arm 标准库、外设驱动程序、用于 FreeRTOS 的外设驱动程序包装器,以及一套齐全的软件样例。在 SDK 分发包的软件样例中,有一对应用程序演示了一种关键的信息交换设计模式,该模式是实现异构计算的基础。

在任何多核计算环境中,单独的处理器都需要有效的机制来传递请求和共享数据。对于 i.MX 8M Mini EVK 应用,NXP 使用的是 RPMsg-Lite——远程处理器消息传递 (RPMsg) 协议的精简版。RPMsg 协议是开放式非对称多处理 (OpenAMP) 框架项目的组成部分,旨在为异构多核系统中多核之间的通信提供标准接口。NXP 的 RPMsg-Lite 解决了小型嵌入式系统中的资源限制,缩小了封装尺寸,并取消了与这些系统不一致的功能。

在 SDK 分发包中,样例应用程序 rpmsg_lite_pingpong_rtos 演示了一次简单的交换,即使用 RPMsg-Lite 实现不同处理器之间的简单 ping-pong 交互(清单 1)。在为另一个“远程”处理器创建 RPMsg 队列 (my_queue) 和端点 (my_ept) 后,“主机”应用处理器向远程内核发送信号。在收到来自远程内核的握手响应后,主机处理器将开始执行一个循环,该循环使用阻塞策略等待远程内核的“ping”消息,然后再发送自己的“pong”响应。

void app_task(void *param) {

。..my_rpmsg = rpmsg_lite_remote_init((void *)RPMSG_LITE_SHMEM_BASE, RPMSG_LITE_LINK_ID, RL_NO_FLAGS); while (!rpmsg_lite_is_link_up(my_rpmsg))

;

PRINTF(“Link is up!\r\n”);

my_queue = rpmsg_queue_create(my_rpmsg);

my_ept = rpmsg_lite_create_ept(my_rpmsg, LOCAL_EPT_ADDR, rpmsg_queue_rx_cb, my_queue);

ns_handle = rpmsg_ns_bind(my_rpmsg, app_nameservice_isr_cb, NULL);

rpmsg_ns_announce(my_rpmsg, my_ept, RPMSG_LITE_NS_ANNOUNCE_STRING, RL_NS_CREATE);

PRINTF(“Nameservice announce sent.\r\n”);

/* Wait Hello handshake message from Remote Core.*/

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, helloMsg, sizeof(helloMsg), NULL, RL_BLOCK);

while (msg.DATA 《= 100)

{ PRINTF(“WaiTIng for ping.。.\r\n”);

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, (char *)&msg, sizeof(THE_MESSAGE), NULL,

RL_BLOCK);

msg.DATA++; PRINTF(“Sending pong.。.\r\n”);

rpmsg_lite_send(my_rpmsg, my_ept, remote_addr, (char *)&msg, sizeof(THE_MESSAGE), RL_BLOCK);

} PRINTF(“Ping pong done, deiniTIalizing.。.\r\n”);

rpmsg_lite_destroy_ept(my_rpmsg, my_ept);

my_ept = NULL;

rpmsg_queue_destroy(my_rpmsg, my_queue);

my_queue = NULL;

rpmsg_ns_unbind(my_rpmsg, ns_handle);

rpmsg_lite_deinit(my_rpmsg);

msg.DATA = 0; 。..}

列表 1:这个片段来自 MCUXpresso 软件开发工具包提供的样例代码,演示了在异构多核处理器中不同处理器间实现交互的基本设计模式。(代码来源:NXP Semiconductors)

开发人员可以基于这一简单的交换,轻松创建完整 *** 作,以跨越多个处理器分配任务执行。另一个样例应用程序 sai_low_power_audio 实质上将 RPMsg-Lite 用作更高层简化型实时消息传递 (SRTM) 应用协议的低级数据链路层。在此应用程序中,Arm Cortex-A53 处理器使用该 SRTM 协议请求 Arm Cortex-M4 处理器播放共享存储器中的音频文件。在控制了共享缓冲区之后,M4 将执行多项 *** 作,最终执行智能直接存储器访问 (SDMA) 事务,以将数据传输到适当的代码,最后传输到串行音频接口 (SAI) 进行音频输出。在执行这些 *** 作期间,A53 内核可以进入低功耗模式。尽管在设计上比 ping-pong 应用程序更复杂,但 sai_low_power_audio 样例应用程序演示了开发人员如何能够使用异构多核处理器来实现性能最大化,同时充分降低智能产品的功耗。

总结

智能产品正在将传统的实时嵌入式处理系统与强大的应用处理能力结合在一起。然而,开发人员需要在满足这些处理要求的同时,还要满足人们对于电池和线路供电型系统中低功耗产品的持续预期。

NXP i.MX 8M Mini 应用处理器采用先进的半导体工艺制造,既可提供高性能异构多核处理能力,又能保持低功耗。使用 NXP i.MX 8M Mini 器件,开发人员可以更好地满足日益复杂的智能产品中的嵌入式系统设计对于高性能计算的新兴需求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)