随着物联网 (IoT) 逐渐需要执行更为复杂的任务,物联网端点的存储器需求随之增加,尤其是执行高级边缘计算的端点。不过,片上微控制器闪存的上限约为 1 兆位 (Mbit),而许多高端物联网端点的存储器需求通常是其数倍之多。

传统的解决方案是利用外部闪存芯片扩展微控制器的程序存储器,但是存储器要求高达 8 Mbit 或更大时,往往就必须使用片外存储器。

因此,在许多情况下,设计人员最好干脆忽略片上闪存,而使用无闪存微处理器(即无 ROM 微控制器),搭配外部高速八线 SPI 芯片内执行 (XiP) 闪存芯片,从而显著降低微控制器成本,同时加强可扩展性以提高设计保障。由于增加了高速八线存储器接口,因而无需再担心存储器访问时间。

本文介绍了无 ROM 微控制器和外部存储器,探讨了在需要大容量程序存储器的物联网端点和嵌入式系统中如何使其成为可行选择。此外,本文还以 NXP Semiconductors 的无 ROM 微控制器和 Adesto Technologies 的八线 SPI XiP 闪存芯片为例,介绍了如何应用这一概念。

物联网边缘端点的存储器扩展

中低性能的物联网端点大多使用微控制器来管理端点,固件存储在片上闪存中。由于增加了额外的应用代码、无线 IP 通信堆栈和增强安全代码,因而固件也需扩展。代码扩展可以在开发阶段进行,也可在现场更新时实现。

如今,部分物联网端点需要执行更多计算功能。这些物联网端点需要执行传感器融合算法、数据插值、模式或图像识别,以及日益复杂的人工智能 (AI) 计算等复杂任务,而非只是通过网络将原始或部分处理的传感器数据传输至中央计算机进行处理。

因此,中央计算机仅仅只接收物联网节点的本地处理结果,而非原始传感器数据的所有字节,从而减少无线网络流量。射频发射器可能是物联网端点中功耗最大的组件,因此边缘计算往往可以延长电池供电端点的电池续航时间。

除此之外,需要现场更新的系统还面临其他存储器挑战。常规系统的存储器需求至少是预估程序存储空间的两倍,以便处理现场更新。这样既能包含现有的程序存储器,又可处理所有无线 (OTA) 更新。某些系统可能需要预估程序存储空间的三倍,剩余的存储器分配给只读出厂固件镜像。若检测到黑客攻击或出现固件镜像损坏等特定类型的系统故障,系统则可以加载出厂固件镜像以恢复系统。

对于某些应用,存储器扩展很快就会超过 1 Mbit 的嵌入式闪存上限,因而必须扩展外部存储器。过去采用的解决方案是添加外部并行闪存芯片。不过,这一方案的缺陷是会占用微控制器约 36 个外部引脚,否则这些引脚就可用于应用 I/O。此外,这也浪费了印刷电路板空间,增加了电路板电磁干扰 (EMI) 的可能性。

SPI 程序存储器扩展

除了使用并行总线外,还可使用串行外设接口 (SPI) 扩展程序存储器。传统 SPI 只用一条数据线路进行半双工单比特传输,但是近年来,该接口已发展为支持两条和四条数据线路,从而使数据吞吐量相应增加,最终使得连接大容量外部 SPI 闪存芯片成为可行之举。

对于程序存储器应用,传统的双线或四线 SPI 使用阴影闪存配置,将外部数据闪存复制到嵌入式静态随机存取存储器 (SRAM),再映射至程序存储空间。这样既能轻松扩展程序存储器,又可由高速 SRAM 运行以提高执行速度。虽颇具优势,却也不乏缺点。由于闪存将根据需要复制到内部 SRAM,而内部 SRAM 容量有限,因此存储器需以分页模式访问。尽管增加片上 SRAM 能克服这一瓶颈,但对于任何半导体而言,SRAM 都是最昂贵的模块之一,因而此举的缺点在于会显著增加微控制器成本。

近来,SPI 已经演变成 XiP。SPI XiP 允许微控制器 CPU 直接通过外部 SPI 闪存执行固件代码。在 SPI XiP 接口添加缓存可大幅提高程序执行速度。

最近,SPI XiP 的广泛应用促使演化出支持八条数据线路的接口。这种八线 SPI XiP 接口的吞吐量显著提高,运行速度远高于片上闪存,高达 100 Mbit/s 以上。

SPI 存储器革命

这引发了一场倒退 30 年的不寻常演变。试想一下,某系统具有 1 Mbit 的片上闪存,以及可由八线 SPI XiP 接口访问的 32 Mbit 外部程序闪存。容量如此小的片上程序存储器引出了一个问题:若移除片上微控制器闪存,仍算是高性价比的系统吗?

一直以来,人们普遍认为相较于具有外部闪存芯片的无闪存微控制器,使用闪存微控制器的中等性能系统性价比更高。直到近年,这一观念才有所转变。

如果移除片上闪存,自然会降低微控制器成本。经深入研究调查表明,若不再需要片上闪存,则仅用于闪存的工艺技术特性也可舍弃,从而降低制造工艺成本,进一步降低微控制器成本。于是,大约 30 年前推出的“无 ROM”微控制器又重现于世。现如今,我们称之为无闪存微控制器。

(重新)引入无闪存微控制器

NXP Semiconductors 的 MIMXRT1052DVL6B (RT1052) 是一款能够充分利用闪存速度的高性能无闪存微控制器。RT1052 是 NXP 的 i.MX RT1050 处理器系列产品之一,基于 600 MHz 的 Arm® Cortex®-M7,具有 32 KB 的指令缓存和 32 KB 的数据缓存。这款微控制器移除了闪存,采用高速 CMOS 工艺技术不受内部闪存限制,从而实现 600 MHz 的时钟速度。RT1052 具有高达 512 KB 的大容量 SRAM,可分区作为程序或数据存储器使用。

该微控制器具有各种高端外设,包括 LCD 接口、支持高端相机的数码相机传感器接口 (CSI) 和像素处理流水线 (PXP)、用于数字音频的 SPDIF 接口、两个 USB OTG 接口、两个 eMMC/SD 闪存卡接口、两个 20 通道模数转换器 (ADC) 和一个加密模块。完整的外设列表如框图所示(图 1)。

图 1:NXP 的 RT1052 具有各种高端外设,包括 SPI XiP 串行接口并支持数据加密。(图片来源:NXP)

另一个选择是 NXP 的 MIMXRT1051DVL6B (RT1051)。这款微控制器的功能与 RT1052 完全相同,但不具备 LCD 接口、CSI 和 PXP。

RT1052 具有 FlexSPI 接口,可使用双线、四线或八线 SPI XiP 闪存接口执行代码。为了增加固件的安全性,该微控制器支持通过 SPI XiP 连接加密程序存储器,Adesto Technologies 的 ATXP032-CCUE-T 就是一个典型的加密存储器实例。

新型 XiP 闪存 *** 作

Adesto 的 ATXP032-CCUE-T 是一款 32 Mbit 八通道闪存芯片,八条数据线路支持双通道传输速率 (DTR) 模式下数据传输高达 266 MB/s,远高于片上微控制器闪存。该闪存由 1.8 V 单电源供电,典型八线模式待机电流为 35 µA,支持的最高 SPI 时钟速度为 133 MHz。

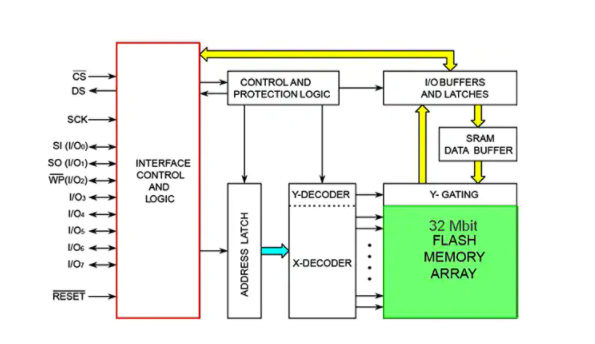

图 2:Adesto 的 ATXP032-CCUE-T 闪存使用八线 SPI(I/O0 至 I/O7)与微控制器连接。SRAM 写数据缓冲区可提高写入闪存 *** 作的性能。(图片来源:Adesto Technologies)

在有效读取闪存期间,ATXP32 电流消耗为 142 µA/MHz,外加 1 mA 电流开销(典型值)。八线模式下,最高 SPI 时钟速度为 133 MHz,电流消耗仅为 19.9 mA。

此外,ATXP032-CCUE-T 还支持标准 SPI 模式 0 和 3,以及四线 SPI 模式。256 字节的安全寄存器包含 128 字节出厂设置的唯一标识符,以及 128 字节的一次性可编程 (OTP) 存储器,后者可用于存储以太网介质访问控制 (MAC) 地址或安全密钥等设备信息。

ATXP032-CCUE-T 的存储器布局值得注意,共分为四个存储体,单个容量为 8 Mbit。内部逻辑已预先配置,因此主机微控制器可在某个存储体中执行代码,而在另一个存储体中编程或擦除。这项 *** 作对主机微控制器是透明的,无需特殊配置设置。

此外,ATXP032-CCUE-T 还有三个状态和控制寄存器,可用于配置低功耗模式等器件工作参数,启用或禁止 DTR 模式,以及设置标准、四线或八线 SPI 模式(默认为标准 SPI)。通过读取状态寄存器,可以指示编程或擦除 *** 作状态、低功耗状态,以及是否有任何存储器设置为写保护。

将无闪存微控制器与外部 XiP 连接在一起

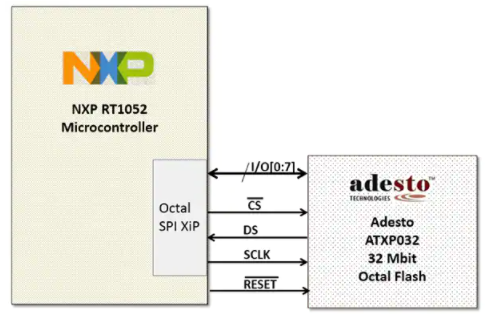

将 RT1052 与 ATXP032-CCUE-T 连接在一起相当简单(图 3)。上电后,RT1052 开始在 96 KB 的片上引导 ROM 中执行代码。引导 ROM 读取 14 个引导模式配置引脚的状态,这些引脚可用于选择 RT1052 多个外部存储器接口之一以连接程序存储器。可选接口包括外部 eMMC 卡、micro SD 卡、常规外部并行接口和 SPI XiP(本例中使用 Adesto 的 ATXP032-CCUE-T)。

图 3:NXP RT1052 无闪存微控制器具有八线 SPI XiP 接口,可轻松连接 Adesto ATXP032-CCUE-T。八线 SPI XiP 接口的 *** 作对 Arm 内核是透明的。(图片来源:Digi-Key Electronics)

RT1052 引导选项还包括从 USB OTG 或 UART 下载代码并由 SRAM 执行。此外,在制造过程中,也可通过熔断 RT1052 的内部保险丝来设置引导模式选项,而非使用引导模式配置引脚。只要 RT1052 的引导 ROM 启用八线 SPI XiP 接口用于程序存储器执行,程序就会立即执行。接着,Arm 内核会从 Adesto ATXP032-CCUE-T 执行固件,其方式与从外部并行闪存设备或内部闪存相同。

由于涉及高速数据传输,八通道串行闪存应放置在印刷电路板上尽可能靠近微控制器八线 SPI XiP 端口的地方。为了减少干扰,印制线长度不应超过 120 mm。与时钟信号的距离应至少是印刷电路板印制线宽度的三倍,并且远离其他信号以避免干扰。I/O[0:7] 双向数据信号间距应保持在 10 mm 以内,以避免偏移。

总结

鉴于对边缘计算、OTA 更新及相关存储器扩展性的需求,物联网端点的存储器需求随之增加。在某些情况下,设计人员可能会发现在这些端点设备中使用无闪存微控制器是不错的选择。

如上所述,无闪存微控制器、高速接口和八线 SPI XiP 闪存芯片的进步,为开发人员提供了构建高性能、高性价比的物联网端点或嵌入式系统的新选项,从而替代传统基于闪存的微控制器方法。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)