数字信号处理器(digital signal processor,DSP)是一种用于数字信号处理的可编程微处理器,它的诞生与快速发展,使各种数字信号处理算送得以实时实现,为数字信号处理的研究和应用打开了新局面,提供了低成本的实际工作环境和应用平台,推动了新的理论和应用领域的发展。目前,DSP技术在通信、航空、航天。雷达、工业控制、医疗、网络及家用电器等各个领域都得到了广泛应用。

1.1 DSP系统和芯片的结构特点

1.1.1 DSP系统的基本结构

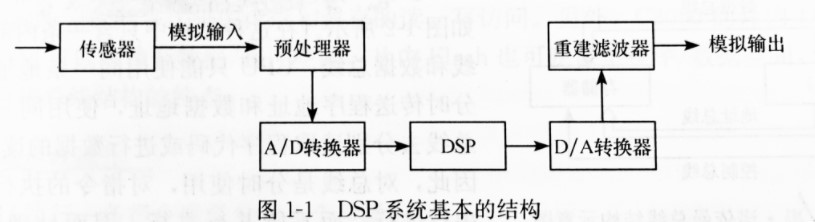

通过传感数将非电物理量转换为模拟电信号,预处理一般包括放大器和滤波器两部分,信号经过放大器的放大变为具有一定幅值的模拟输入信号,而滤波器(低通或带通)的作用则是滤除输入模拟信号中的无用频率成分和噪声,避免采样后发生频谱混叠失真。A/D转换器的任务是在满足奈奎斯特采样定理的条件下,将模拟信号转换为数字信以,DSP负责对输入数字信号进行某些算法,如卷积、相关、滤波或快速傅里叶变换(FFT)等。经过处理之后的数字信号再进行DA转换,由于转换输出的模拟信号中含有许多高频成分,因此要通过重建滤波器滤除这些高频信号,以获得平滑的模拟输出信号。

实际上,为了完成数字信号处理的任务,除了图1-1所示的DSP基本结构之外,还必须在DSP系统中配置人机接口、存储器、通信接口、测试接口和电源设备等。

1.1.2 DSP芯片的结构特点

1.采用改进型哈佛结构

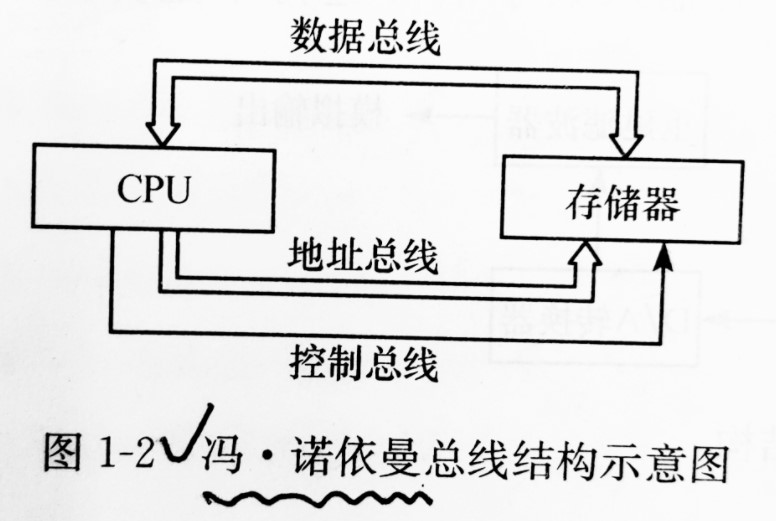

计算机的总线结构分为:冯·谐依曼(von Neumann)结构和哈佛(Harvard)结构。

多数微处理器和单片机采用冯·诺依曼结构,线和数据总线,CPU只能使用同一条地址总线去如图1-2所示。(在这种结构中只含一条内部地址总分时传送程序地址和数据地址,使用同一条数据总线去分别读取程序代码或进行数据的读写访问)因此,对总线是分时使用,对指令的执行也只能串行进行,而不能并行进行,因而处理速度慢,数据吞吐量低。(程序和数据共用同一套总线,对程序和数据需分时续写)

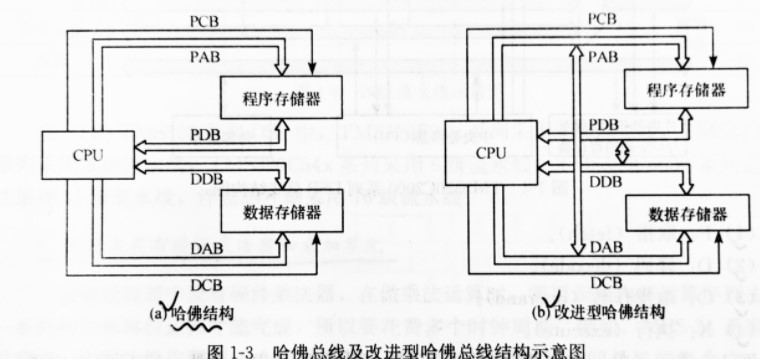

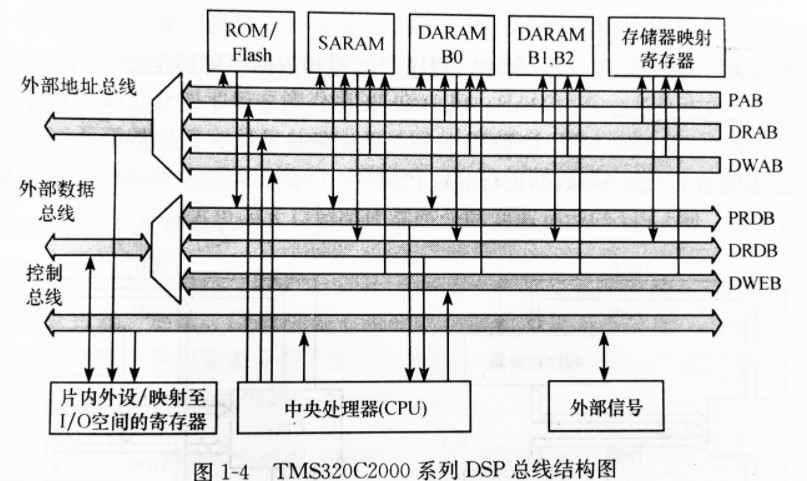

哈佛总线结构如图1-3(a)所示,程序存储器和数据存储器是分开的,有多条独立的程序总线和数据总线,其中PAB、PDB和PCB分别是程序地址总线、程序数据总线和程序控制总线,DAB、DDB和DCB分别是数据地址总线、数据数据总线和数据控制总线,它们可同时对程序和数据进行寻址和读写,因此,使指令的执行和对数据的访问能够并行进行,使CPU的运行速度和处理能力都得以大幅度提高。

DSP采用的是进型哈佛总线结构如图1-3(b)所示。其改进之处是:在数据总线和程序总线之间有局部的交叉连接,也就是说,在程序空间和数据空间之间有相互访问的能力,从而增加了存储器访问的灵活性,提高了DSP的运行效率。DSP的哈佛总线改进之处主要体现在下列3点。

⑴片内RAM可以映像数据空间,也可以映像至程序空间当片内RAM被映像至程序空间时,意味着可以利用程序总线来访问数据。

⑵片内ROM可以映像至程序空间,也可以映像至数据空间。当片内ROM被映像至数据空间时,就可利用数据总线去读取程序空间。

⑶具有根装裁(boatloader) 功能,允许将片外的指令代码调至片内数据存储器,供CPIL零等待运行。

2.流水线 *** 作

CPU执行一条指令通常分为4个阶段。

⑴F:取指(fetch)。

⑵D:译码(decode)。

⑶O:取 *** 作数(operand)。

⑷X:执行(execute)。

dsp技术综述 发展现状

所谓流水线 *** 作就是一条指令的不同阶段分在连续的几个周期上,通过不同的硬件去完成指定的不同执行阶段(称为级 )。

3.片内集成有硬件乘法器和乘加单元

一般微处理器中没有硬件乘法器,在做乘法运算时,需要调用内部运算序列去执行一系列相加和移位运算才能完成,所以要花费多个时钟周期。例如,TMS320C54x系列片内集成有一个17位X17位的硬件乘法器和40位的加法器,可以高速完成乘法-累加运算(MAC);TMS320C6000系列片内有2个硬件乘法器,支持在单周期内完成16位×16位、16位×32位的乘法,并支持双16位×16位和4个8位×8位的乘法运算。

4.功能强大的CPU结构

除了上面提到的硬件乘法器和乘加单元,DSP的CPU一般还包括:算术逻辑运算单元(ALU)、累加器、加法器、桶型移位器、程序地址产生和数据地址产生等部分。

5.硬件循环重复机制

许多DSP芯片具有重复 *** 作指令和支持重复 *** 作的专用硬件,通过它们可以自动地重复执行单条指令或一段指令。

6.复合 *** 作指令

所谓复合 *** 作是指在一条单字单周期指令中可以分别完成多个 *** 作任务。

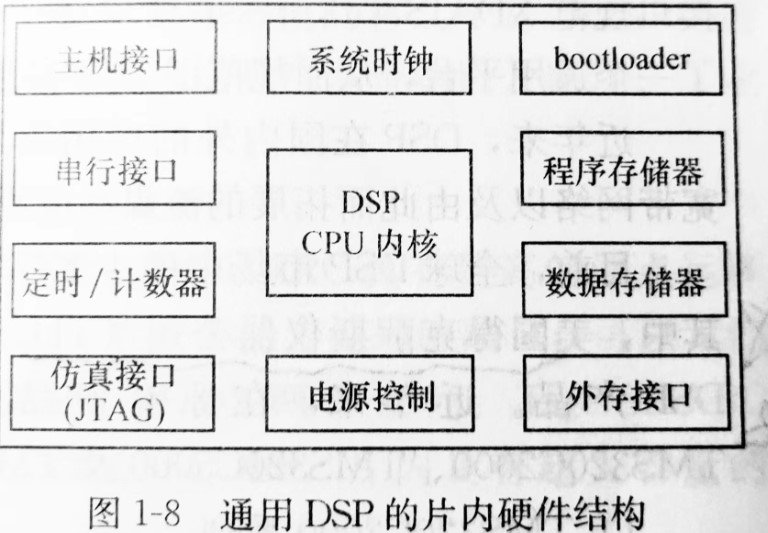

7.嵌入式功能

DSP片内配置有大量片内外设,如图1-8所示。一般包括程序存储器、数据存储器、定时/计数器、串行口、主机接口、外部存储器接口、电源控制、JTAG接口等。开发者不用外扩很多器件,既可组成独立的应用系统。DSP芯片具有很强的扩展接口的能力,可无缝连接片外存储器和一系列I/O器件。由于DSP既有高速的数字信号处理能力,又有强大的嵌入式接口能力,因此在嵌入式系统中获得了广泛应用。

DSP技术的发展

1.3DSP芯片的分类、性能及其应用

1.3.1 DSP芯片的分类填题

1、按照数据格式分类

按照数据格式分为定点DSP和浮点DSP。

2、按照芯片用途分类

按照芯片用途分为通用型DSP和专用型DSP。

3、按照芯片结构分类

按照芯片的结构有多种分类法。例如,静态DSP是指在某种颇率范围内的任问题率上都能正常工作的DSP芯片,除运行速度有变化外,没有性能的下降:一致性DSP是指它们的指令集、CPU结构及管脚都相互兼容的DSP芯片,如TI公司的TMS320系列DSP等。

为某种应用且的而专门设计的ASIC系统,它只涉及一种或一种以上的自然类型数据的处理,如音频、视频、语音的压缩和解压缩、调制和解调器等,其内部部是由基本DSP运算单元构建的,包括FIR、11R、FFT、DCT和卷积码的编码/解码器及RS编码/解码器等。其特点是计算密集、数据量和运算量都很大。

积木式结构由乘法器、存储器、控制电路等单元逻辑电路搭接面成,这种结构方式也称为硬连线逻辑电路,具有成本低、速度高等特点,但没有可编程能力。目前主要用于接收机的前端的某些高频 *** 作中。

1.3.2DSP芯片的性能

DSP芯片种类繁多,结构差别很大,使用场合有所不同,因此,目前对DSP性能优劣的衡量还没有一个统一的标准。不同厂商的产品指标甚至不具备可比性。下述技术指标只是从运算速度的角度描述了DSP的处理能力或性能,仅作为系统设计时的一种参考。

(1)MIPS,百万条指令/秒。例如,TMS320C6416在时钟为1GHz时的峰值性能可达8000MIPS。

(2)MOPS,百万次 *** 作/秒。 *** 作包括CPU *** 作、地址计算、数据访问及I/O *** 作等,该项指标用于评价DSP的处理能力。如 TMS320C6201在时钟为200MHz时的峰值性能可达2400MOPS。

(3)MFLOPS,百万次浮点 *** 作/秒。浮点 *** 作包括浮点乘法、加法、减法、浮点数据的存储等 *** 作。该项指标是衡量浮点DSP处理能力的重要指标。如ADSP-TS201S的峰值性能可达14400MFLOPS。

(4)MBPS:百万位/秒。该项指标用于衡量DSP的数据传输能力,通常指总线或1/O口的带宽,它是对总线或I/O口数据吞吐率的量度。如TMS320C6000的总线时钟为200MHz时,其总线数据吞吐率为800MBPS。

(5)MAC执行时间:完成一次乘法累加运算所需要的时间。大部分DSP可在单周期内完成一次MAC。

(6)FFT执行时间:完成一个N点FFT运算所需要的时间。FFT是数字信号处理中的典型运算,因此用FFT执行时间作为DSP的性能衡量标准更具有实用价值。

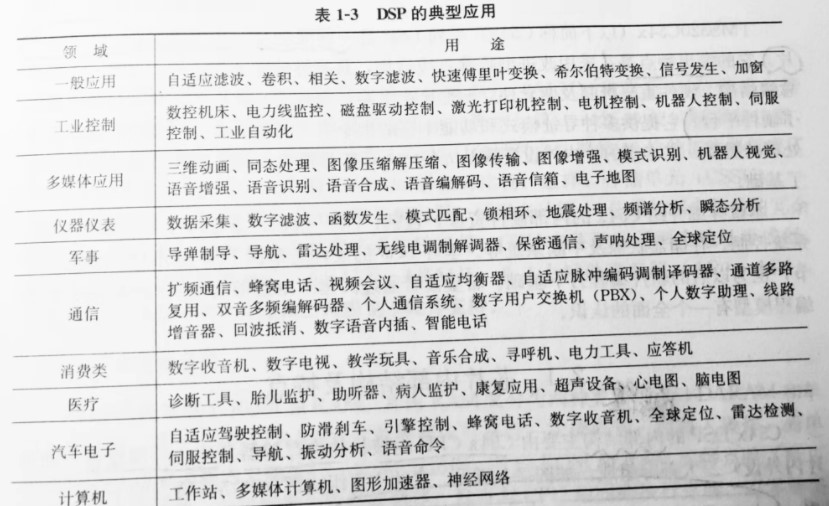

1.3.3DSP芯片的应用

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)