启动 mqSemi 引入了单点源 MOS (S-MOS) 单元设计,适用于基于功率 MOS 的设备。S-MOS 技术采用 Silvaco Victory 工艺和器件软件在 1200V SiC MOSFET 结构上采用和实施。提供了一整套静态和动态结果,用于将 S-MOS 与使用平面和沟槽 MOS 单元设计的标准SiC MOSFET 2D 结构进行比较,如参考文献中所定义。

随着时间的推移,MOS 单元制造和设计平台显着提高了功率 MOSFET 和绝缘栅双极晶体管 (IGBT) 等硅基功率器件的性能。在这两种器件中,平面或沟槽 MOS 单元都以蜂窝或线性模式分组。

硅基 MOS 器件的结果可用于制造需要高单元封装密度的 SiC 功率 MOSFET。近年来,人们提出了先进的 3D 设计方法来改进设备的静态和动态特性。利用多维通道宽度来提高单元密度并最小化 RDS(通态电阻)的低压 FinFET 单元架构连接到这些 3D 拓扑 (ON)。

采用 SiC 作为功率器件材料的优点之一是能够使用许多众所周知的硅器件原理和制造程序。基本器件拓扑包括垂直肖特基二极管或垂直功率 MOSFET(在通过 JFET 适当分流后)。

因此,许多用于保持硅器件长期稳定性的工艺也可以用于保证 SiC 器件的长期稳定性。然而,仔细观察发现,基于 SiC 的器件需要比基于 Si 的器件进行额外且不同的可靠性测试,例如材料的独特性能和缺陷、更大的带隙和更高的电场,特别是在结终端区域,以及在更高的温度和开关频率。

S-MOS 电池概念

与这种三维结构趋势相吻合的是由初创公司mqSemi开发的“Singular Point Source”MOS单元概念(也称为S-MOS)。mqSemi 由 Munaf Rahimo 和 Iulian Nistor 创立,总部位于瑞士,致力于开发先进的功率半导体概念,解决用于电动汽车、汽车和可再生能源等应用的下一代电力电子系统。mqSemi 在过去两年中申请了 20 多项专利,已经进行了大量的模拟,现在已准备好进入原型制作阶段。mqSemi 团队在 IGBT 方面获得的多年经验和知识,对解决碳化硅 MOSFET 的关键问题有很大帮助;例如降低损耗、提供稳健的短路模式和阻断行为、栅极驱动控制和高频振荡。

mqSemi 的发言人 Rahimo 和 Nistor 表示:“我们相信,对于一个可持续发展的世界,我们将需要基于高效、紧凑、可靠和具有成本效益的功率半导体器件的应用,这些器件是技术领先和以创新为中心的。”

S-MOS 的好处是双重的:一方面,它使用独特的方法精心定义了总通道宽度,也称为通道面积;另一方面,它可以实现更高的 MOS 单元封装密度。此外,S-MOS 概念可以在 MOSFET 和 IGBT 上实现,从而提高开关性能,同时实现更高的效率和更低的整体损耗。

S-MOS 单元与标准平面单元和沟槽 MOS 单元的不同之处在于如何设计每个器件面积的总沟道宽度(W ch参数)。如图 1a 和图 1b 所示,平面或沟槽 MOS 单元的沟道宽度 W ch定义为 N++ 源极周围的总外围距离,它还取决于 MOS 单元排列的几何形状(线性或蜂窝布局设计)。S-MOS 单单元沟道宽度 W ch,如图 1c 所示,由 N++ 源极和 P沟道结 W PNJ长度的小尺度尺寸定义。通过将这个小的几何特征定位在沟槽侧壁上,预定的单位沟道长度 W chn提供。对于 S-MOS,N++ 和 P通道轮廓类似于平面单元的轮廓,但位于沟槽侧壁上。因此,总沟道宽度取决于每个芯片的门控沟槽侧壁的总数。如图 1c 底部所示(红色虚线),N++/P通道结的形状可以近似为“四分之一圆”,单个沟槽的 W chn尺寸约为 150-300 nm侧壁。给定芯片面积的总 W ch可以作为所有沟槽侧壁上所有 W chn的总和获得。

图 1:源 MOS 单元概念

The S-MOS concept has been demonstrated by means of 2D and 3D TCAD simulaTIons conducted on 1200V SiC MOSFETs, including the S-MOS and reference planar and trench structures.

“During the simulaTIon, we found a very special feature, that we were not expecTIng, on the side-wall of a trench, where we could get the so called channel width which defines the total channel density which was something based on a diffusion profile”, said the speaker at mqSemi.

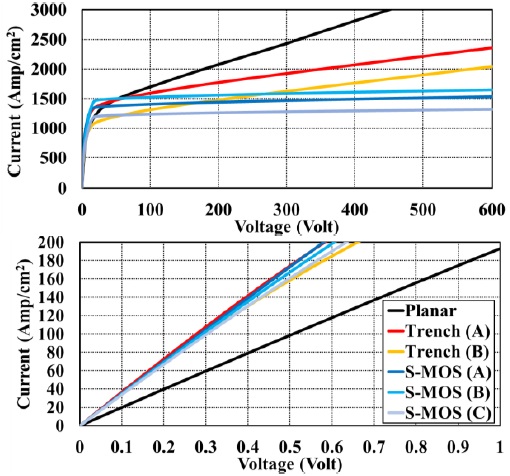

The simulaTIon was peformed on a 1200V SiC MOSFET because the static losses, measured by Rds(on), are not difficult to assess. The same technology can be applied to different voltage classes, as well. Static and mixed mode inductive load dynamic simulations were carried for all device structures (S-MOS, Trench and 2D Planar) which were scaled for a total active area of 1cm2. The output voltage-current characteristics obtained with the simulation are shown in Figure 2; the upper image refers to a voltage range up to 600V, while the lower image is a zoom-in up to 1V at Vgs=15V and 150°C. The S-MOS concept has provided low Rdson levels (around 3 mΩ-cm2 在 150°C),类似于沟槽电池。然而,如图 2 所示,与其他参考模型相比,S-MOS 还提供平坦的饱和电流。

图 2:1.2kV SiC MOSFET 输出曲线,Vgs=15V,150°C

“我们发现我们有更好的切换可控性,这就是进入第三维的全部想法。与沟槽电池相比,我们获得了大大降低的开关损耗,并且我们有更多的设计自由度来进一步优化它并获得更高的电池密度”,mqSemi 的发言人说。

在 150°C 下对所有器件的短路电流进行了仿真,显示了 S-MOS 如何表现出更少的短沟道效应并改善了传导损耗和短路性能之间的权衡。尽管 S-MOS 概念仍需要进一步的设计优化,但所展示的性能非常有前途,在 mqSemi,他们认为已经为下一阶段做好准备,即原型设计。

审核编辑:刘清

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)