I2C协议已经用了很多了,但是呢,在硬件设计方面,基本也是只会抄抄电路,并没有理解其中的原理和细节。这一章我们具体要说说需要怎么设计I2C电路。

1. 什么是I2C?

I2C Bus(Inter-Integrated Circuit Bus) 最早是由Philips半导体(现被NXP收购)开发的两线时串行总线,常用于微控制器与外设之间的连接。这里要注意IIC是为了与低速设备通信而发明的,所以IIC的传输速率比不上SPI。

1.1 硬件连接

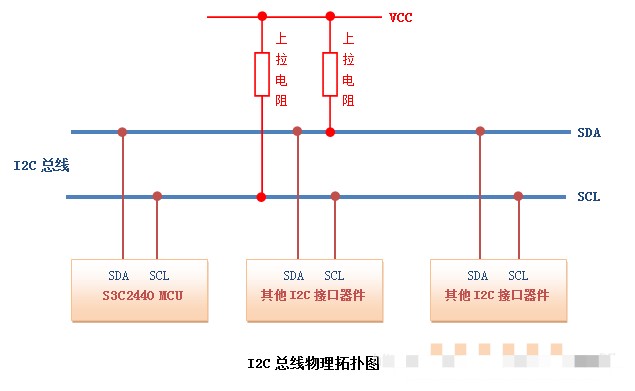

I2C仅需两根线就可以支持一主多从或者多主连接,I2C使用两个双向开漏线,配合上拉电阻进行连接,关于上拉电阻阻值大小有最大值和最小值的限制,具体计算请参考: IIC上拉电阻的计算. I2C由于内部是OD门,所以一定需要上拉电阻!!!

上拉电阻的经验值为:

通信速率小于10K时, 上拉电阻选10K

通信速率在10K~400K时,上拉电阻选4.7K

通信速率大于400K时,上拉电阻选2.2K

1.2 多I2C器件硬件连接

如下图所示, 多器件相连接时, 只需要将对应的SCL和SDA相连接就可以了, 那么主设备时怎么和从设备进行通信的呢?每个I2C器件都有器件地址选择单元, 可以通过设置每个器件的器件地址来和相应的设备通信。

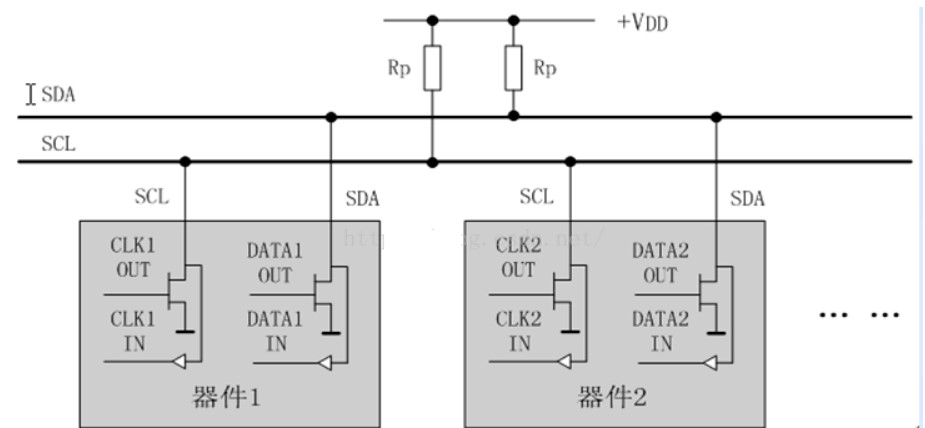

1.3 I2C器件内部结构

漏极开路(Open Drain)即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态,若需要产生高电平,则需使用外部上拉电阻

高阻状态:高阻状态是三态门电路的一种状态。逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。电路分析时高阻态可做开路理解。

我们知道IIC的所有设备是接在一根总线上的,那么我们进行通信的时候往往只是几个设备进行通信,那么这时候其余的空闲设备可能会受到总线干扰,或者干扰到总线,怎么办呢?

为了避免总线信号的混乱,IIC的空闲状态只能有外部上拉, 而此时空闲设备被拉到了高阻态,也就是相当于断路, 整个IIC总线只有开启了的设备才会正常进行通信,而不会干扰到其他设备。

IIC器件地址: 每一个IIC器件都有一个器件地址,有的器件地址在出厂时地址就设定好了,用户不可以更改,比如OV7670的地址为0x42。有的器件例如EEPROM,前四个地址已经确定为1010,后三个地址是由硬件链接确定的,所以一IIC总线最多能连8个EEPROM芯片。

1.4 I2C协议层

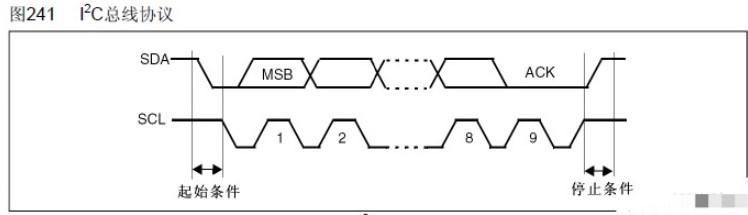

I2C 总线在传送数据过程中共有三种类型信号, 它们分别是:开始信号、结束信号和应答信号。

开始信号: SCL 为高电平时,SDA 由高电平向低电平跳变,开始传送数据。

结束信号: SCL 为高电平时,SDA 由低电平向高电平跳变,结束传送数据。

应答信号: 接收数据的 IC 在接收到 8bit 数据后,向发送数据的 IC 发出特定的低电平脉冲,表示已收到数据。CPU 向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU 接收到应答信号后,根据实际情况作出是否继续传递信号的判断。若未收到应答信号,由判断为受控单元出现故障。

这些信号中,起始信号是必需的,结束信号和应答信号,都可以不要。

这章以硬件设计为主,软件协议简单带过

1.5 I2C协议特点

IIC主要特点:

通常我们为了方便把IIC设备分为主设备和从设备,基本上谁控制时钟线(即控制SCL的电平高低变换)谁就是主设备。

IIC主设备功能:主要产生时钟,产生起始信号和停止信号

IIC从设备功能:可编程的IIC地址检测,停止位检测

IIC的一个优点是它支持多主控(mulTImastering), 其中任何一个能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率。当然,在任何时间点上只能有一个主控。

支持不同速率的通讯速度,标准速度(最高速度100kHZ),快速(最高400kHZ)

SCL和SDA都需要接上拉电阻 (大小由速度和容性负载决定一般在3.3K-10K之间) 保证数据的稳定性,减少干扰。

IIC是半双工,而不是全双工 ,同一时间只可以单向通信

为了避免总线信号的混乱,要求各设备连接到总线的输出端时必须是漏极开路(OD)输出或集电极开路(OC)输出。这一点在等下我们会讲解

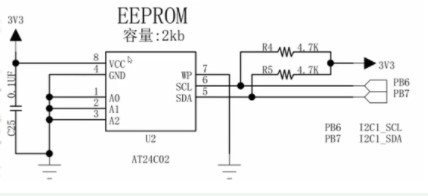

2. AT24C02硬件设计

AT24C0X是常见的IIC协议器件,成本低,大部分板卡都会带。这个外设也比较简单, 需要注意的是,A0 A1 A2管脚用来设置器件地址, 器件地址由这三位构成一个8进制数,所以最多能带8个AT24C0X器件,,而7管脚WP使用来写保护的, 将这个管脚拉低,是关闭写保护,这个器件通信速率不是很高,所以这里只需要接4.7K的上拉电阻就可以了。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)