EJTAG(Enhanced Joint Test AcTIon Group)是MIPS公司根据IEEE 1149.1协议的基本构造和功能扩展而制定的规范,是一个硬件/软件子系统,在处理器内部实现了一套基于硬件的调试特性,用于支持片上调试。

龙芯一号处理器IP核是在龙芯一号处理器基础上,对功耗、面积和性能等各方面进行改进而得到的高度灵活、适用于更广泛领域的处理器内核。它采用RISC架构,可运行MIPS III指令集,支持EJTAG调试功能,采用可配置架构,可在满足用户性能要求的前提下,实现最低成本的产品集成。

1 EJTAG工作机制及实现

1.1 EJTAG组成

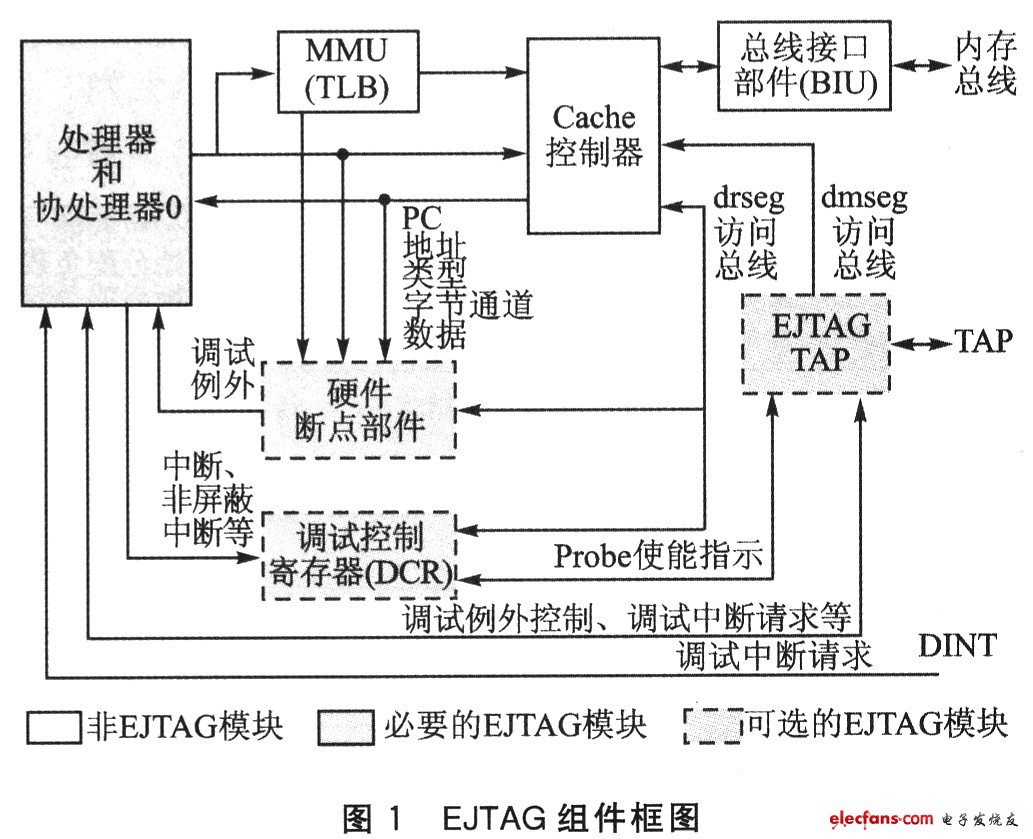

所有MIPS的微处理器或是包含MIPS核的SoC芯片组件均提供对EJTAG调试的支持。EJTAG接口利用JTAG的TAP(Test Access Port)访问方式,将测试数据传入或者传出处理器核。EJTAG可实现的功能包括:访问处理器的寄存器、访问系统内存空间、设置软件/硬件断点、单步/多步执行等。如图1所示,EJTAG调试功能模块由4部分组成:CPU核内部的组件扩展,硬件断点单

元,调试控制寄存器(DCR)以及TAP接口。

1.2 EJTAG工作机制

处理器在某个调试例外(debug excepTIon,如单步运行、断点等)产生以后,进入到调试模式(debug mode),直到DERET指令执行以后从调试模式退出来。在这段时间里,处理器执行调试例外处理过程。在调试例外处理过程中,调试软件通过对TAP处理器的访问 *** 作,实现了对普通寄存器的访问、协处理器的访问、系统内存空间的访问等功能。系统退出调试模式以后允许应用程序或是系统代码继续执行,直到遇到下一个调试例外。重复以上过程,EJTAG实现了单步运行或者多步运行等调试功能。

1.2.1 调试例外

在体系结构的设计上,EJTAG并不需要与CPU紧密结合,但CPU必须提供调试寄存器、进入调试模式和在调试模式下执行指令的能力,更重要的是调试例外的优先级必须高于其他处理器的例外(excepTIon)。EJTAG调试是通过处理器的调试例外来实现的,调试例外将CPU从非调试模式(non-debug mode)转到调试模式。在调试模式下也可以再发生调试例外,这种例外就叫做“调试模式例外(debuIg mode excepTIon)”。

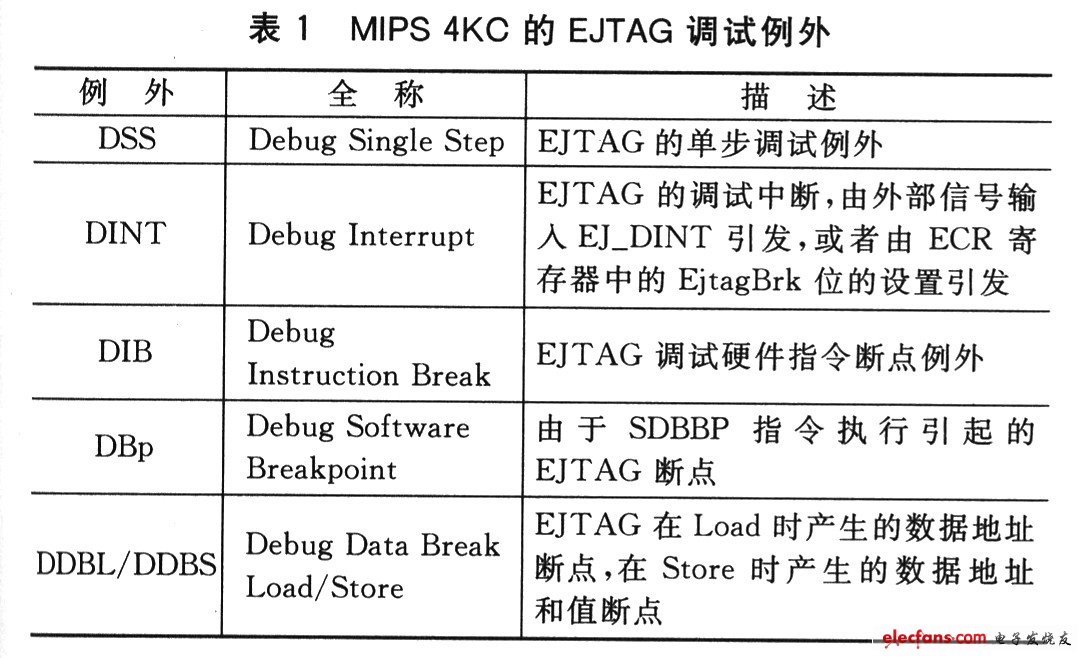

MIPS 4KC处理器提供的调试例外如表1所列。

当CPU执行了软件断点指令(SDBBP),或者发生了单步调试,或者在EJTAG回路中产生了JtagBrk调试事件,或者发生了硬件断点时,CPU就会产生调试例外。SDBBP是一个标准的MIPS指令集指令,软件断点的设置就是调试软件通过把正常的应用程序代码替换成软件断点指令来实现的。EJTAG支持指令断点和数据断点两种类型的硬件断点,指令断点发生在处理器取指过程中,数据断点发生加载/存储传输过程中,它们可以设置在任何地址空间中,包括不能被改写的ROM空间。调试例外发生后,CPU首先屏蔽地址错误异常和中断异常,然后转向调试例外处理程序的执行。调试例外处理程序是由调试软件通过与TAP处理器的配合,利用EJTAG接口实现的。在调试模式下,CPU仍能够正常地访问协处理器和系统内存空间等处理器资源。

调试寄存器包括DEBUG寄存器、DEPC寄存器和DESAVE寄存器,都被定义在协处理器中。DEBUG寄存器保存了CPU进入调试模式的原因,以及同时是否发生了其他CPU例外的标志位,也被用来控制单步运行的设置。DEPC(Debug Exception Program Counter)寄存器保存了发生调试例外时将要执行的那条指令的地址,当退出调试模式后,该地址恢复到PC寄存器中。DESAVE (Debug Exception Save)寄存器是一个草稿寄存器,被调试软件用在对普通寄存器的处理过程中,该寄存器的内容不需要保存。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)