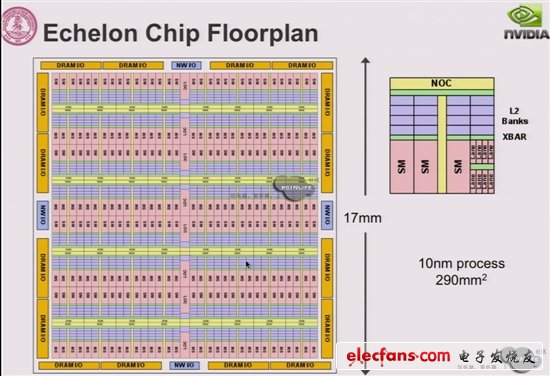

国内硬件网站PCINLIFE的管理员cho于昨日在论坛上公布了一些NVIDIA于几个月前在斯坦福大学展示用的幻灯片,展示了NVIDIA ExaScale计划的核心——Echelon的具体芯片示意图和具体架构等。

从图上可以看出,Echelon芯片和之前我们报道的相似,各个SM模块独立命名为"NoC"(Network on Chip)通过内部界面,经由L2 Cache和内存控制器与其他SM相互连接。有所不同的是,去年在美国西雅图举行的SC10超级计算大会上NVIDIA首席科学家Bill Dally透露的Echelon含128个SM模块,而在这里变成了256个。

其余指标大致相同,每个SM模块里面含8个SM Lane(类似CUDA Core),芯片中间的8个LOC即Latency Processor也就是Project Denver要制造的主要东西。整体芯片面积为17*17约290平方毫米,采用逼近硅芯片极限的10nm制程工艺制造。(看到这里先别说火星,毕竟DARPA给出的时间表是2017/2018年出最终成果)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)