时钟设备设计使用 I2C 可编程小数锁相环 (PLL),可满足高性能时序需求,这样可以产生零 PPM(百万分之一)合成误差的频率。高性能时钟 IC 具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统的子系统,例如处理器、FPGA、数据转换器等。此类复杂系统需要动态更新参考时钟的频率,以实现 PCIe 和以太网等其它诸多协议。

时钟 IC 属于 I2C 从器件,需要主控制器来配置内部 PLL 逻辑,其控制逻辑可以写入微控制器内。作为 I2C 主机,微控制器将配置写入时钟 IC 的内部易失性存储器并控制 PLL。因此,可以通过板上 MCU - IC 组合进行系统时钟频率的动态更新。可编程微控制器为高性能时钟 IC 提供控制逻辑能力,通过减少板载 IC和板上走线使整体设计更加紧凑,并降低最终物料成本。

*** 作理论

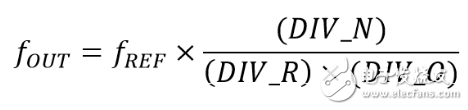

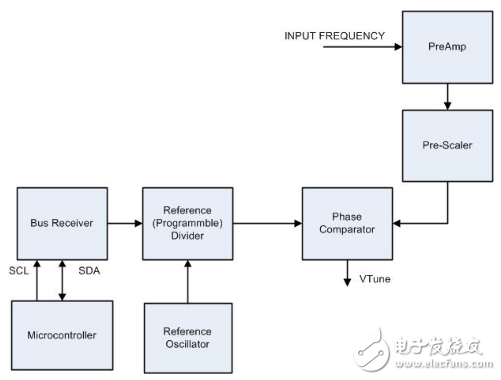

图 1 为高性能时钟设备的基本 PLL 架构。该设计使用比例因子为 PLL 输出端口提供时钟合成。最终输出频率的基本公式为:

fREF 为输入参考晶体频率(在多数应用中通常为 8 MHz 至 48 MHz)。

DIV_R(DIV_R1 和 DIV_R2)是输入频率参考的分频因子。此类分频器名为预分频器。

DIV_N 为小数 N 分频因子。

DIV_O(DIV-O1、DIV-O2、DIV-O3 和 DIV-O4)为输出前的后分频因子。

图 1简化高性能时钟的 PLL 架构框图

图1中的橙色框图为参数,使用这些参数的方程式为可编程方程式。这些参数可以在出厂时写入时钟设备的非易失性存储器。时钟设备具有内部易失性和非易失性存储器,两个存储器互相复制其内容。非易失性存储器在出厂时已被写入所需配置,在最终应用中,当设备启动电源时,非易失性存储器的内容会被复制到易失性存储器。同时,PLL 产生所需的默认时钟输出。

时钟 IC 的重要特性之一就是通过 I2C 接口实现运行时可编程。通过可编程功能,用户可以更改设备的易失性存储器内容以进行即时更改。只需使用适当的 I2C 指令,就可以通过主控制器实现用户配置文件的即时编程功能。

设备的非易失性存储器还可以存储预定义的多用户配置。用户可以使用频率选择 (Frequency Select, FS) 功能以选择其中一个配置。该 FS - 位为设备中可用的 CMOS 输入引脚。FS 引脚应用 N - 位外部 CMOS 信号,然后内部选择存储在非易失性存储器中的一个配置文件,这个配置文件同样也被复制到了易失性存储器,PLL 则输出不同的信号。

同时,微控制器通过 I2C 提供数据来控制高频时钟。使用微控制器的优点是,它具有不同的通信外设和通信协议,如 I2C、SPI、UART、蓝牙、ZigBee 等,使得系统能够以主从配置将数据传输到其他微控制器,也可以使用一个自定义的应用传输至安卓和 iOS 设备。此外,微控制器还配有各种 IDE 工具用于简化设计。这可以更好地证明使用 I2C 指令来配置 PLL 参数、编写并验证定制应用程序是合适的。

高性能时钟的应用需求

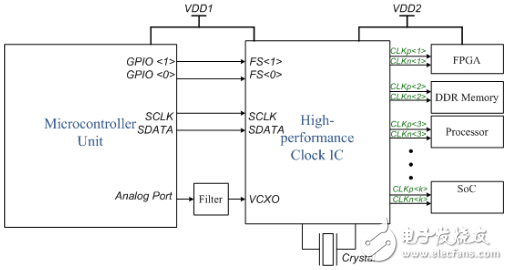

高性能时钟 IC 专为消费者、工业和网络应用而设计。此类时钟 IC 具有多个从不同 PLL 导出的差分输出和单端输出,并且可以通过 I2C 接口实现可编程功能。此外,高性能时钟 IC不仅可以支持 PCI Express (PCIe) 1.0 / 2.0 / 3.0、USB 2.0 / 3.0 和万兆以太网 (GbE)等关键接口标准的参考时钟。还能支持压控晶体振荡器 (VCXO) 和频率选择 (FS)等其他增值功能。

高性能时钟 IC 采用设计实现 I2C 从机模式。因此,需要一个板载 I2C 主机来控制以下可编程功能:

· 通过 I2C 接口进行系统内编程

· 通过频率选择 (FS) 引脚更新配置

· 外部复位 *** 作

· 压控晶体振荡器 (VCXO) *** 作

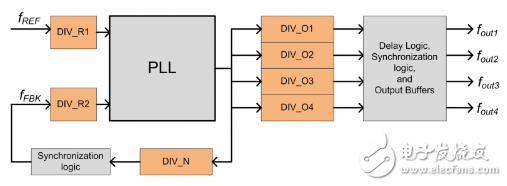

图 2:微控制器 - 高性能时钟接口电路

微控制器在时钟 IC PLL 控制中的作用

如图 2 所示,将时钟 IC 连接到微控制器电路。时钟 IC 具有内部 PLL 模块,其功能是提供作为固定直流电压的调谐电压 (Vtune) ,而调谐电压将随频段而变化。PLL 模块在输入端接收本地振荡器频率,由内部前置放大器放大信号。另外,预分频器对输入频率进行下变频,并将其作为输入传送至相位比较器。

图 3:PLL 模块的微控制器控制。

微控制器通过 I2C 发送数据到可编程分频器。该分频器也接收来自参考振荡器(例如 4 MHz 晶体振荡器)的输入。相位比较器(即相位检测器)通过预分频器接收本地振荡器频率(例如 87.15 MHz),还通过参考分频器和参考振荡器接收微控制器的输入(例如,87.15 MHz)。如果两个输入都匹配,相位比较器将提供 Vtune 调谐电压。一旦本地振荡器频率与微控制器频率数据之间稍有不匹配,都将无法提供调谐电压 (Vtune) 和输出。图 3 所示为完整的框图。

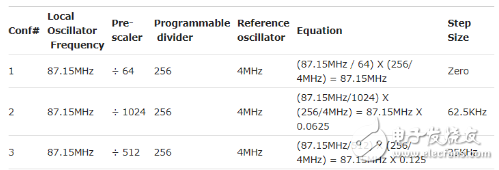

在微控制器的帮助下,PLL 通过调谐本地振荡器频率产生闭环,并在输出端产生调谐电压。调谐电压将从较低频率信道增加到较高频率信道。通过改变预分频器和可编程分频器的值,微控制器可以调整步长。

步长 =(本地振荡器频率/预分频器)X(可编程分频器/参考振荡器)

表 1 所示为部分配置

通过 I2C 接口进行系统内编程

系统内编程可为系统设计实现快速有效的迭代。编程数据序列可通过 SCL 和 SDA 引脚传送到时钟器件,把 *** 作顺序编程至板载微控制器(主设备)中,通过命令和数据在运行时与从机时钟进行交互。

此处为系统示例,其中时钟信号必须以采样率的倍数为准。该时钟频率在 155.52 MHz 和 156.25 MHz 两组频率之间变动。这意味着驱动串行控制器的时钟必须能够在这两个值之间灵活切换。微控制器主设备可以访问并修改写入易失性存储器的 PLL 配置,从而满足这两个频率需求。

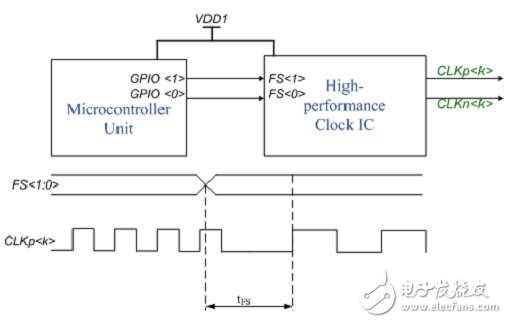

通过频率选择 (FS) 引脚更新配置

高性能时钟设备支持包含个性化配置的多个用户配置文件。在 FS 引脚转换方面,高性能时钟器件具有两个时序规格 - 快速切换和慢速切换。

快速切换适用于输出 ON/OFF 、输出分频值变化,以及输出 MUX 设置更改。慢速切换则适用于更改 PLL 参数(包括 PLL ON/OFF)。顾名思义,快速切换中的输出变化更快,而慢速切换的速度较慢。两种切换类型都可以打开或关闭输出,并且不出丝毫差错。图 4 所示为 FS 与输出时钟之间的时序关系。

图 4:频率选择 *** 作

外部复位 *** 作:

当外部复位生效时,时钟 IC 进入低功耗模式。输出和 I2C 总线信号处于高阻抗 (HI-Z) 状态,直到取消外部复位并完成初始化。外部复位重启易失性存储器内容,存储在非易失性存储器中的配置则被复制到易失性存储器。当需要重新初始化任意一个系统中运行的应用程序时,该功能将被使用。

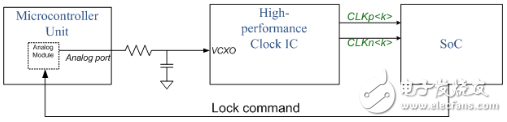

压控晶体振荡器 (VCXO) *** 作:

对某些应用而言,输出时钟频率应通过使用模拟反馈跟踪输入数据流。如图 5 所示,时钟 IC 作为大锁相环的一部分。ASIC 或 SoC 负责跟踪输入流、计算误差并产生 PWM 信号(通常来说),随后将误差信息反馈至本地时钟发生器以进行频率调谐。

图 5VCXO 示例电路

VCXO 功能能够修改 PLL 频率,因此频率牵引不依赖于晶体特性、温度、电压或设备工艺。VCXO 调制是线性、精准调制。也可以使用时钟参考。通过微控制器的内置模拟模块,VCXO 的控制逻辑精准到小数点后 6 位。

作为 I2C 主设备,微控制器将配置写入时钟 IC 的内部易失性存储器并控制 PLL。因此,通过板载 MCU-IC 组合可以实现系统时钟频率的动态更新。开发人员可以使用可编程微控制器,为高性能时钟 IC 提供控制逻辑。这可以减少对板载 IC 和走线数量的需求,使得整个系统设计更加紧凑。

微控制器配备强大 IDE 工具,可以加速应用开发。集成可编程片上系统(PSoC)器件可进一步简化设计并有助于降低整体产品成本。有关高性能时钟 IC 设计的更多详细信息,请参阅4-PLL扩频时钟发生器入门以及扩频时钟发生器的设计最佳实践。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)